## 2-Bit Bidirectional Voltage-Level Translator for Open-Drain and Push-Pull Applications

#### **FEATURES**

- Voltage Level Translator Without Direction-Control Signal

- Maximum Data Rates

- 24Mbps (Push Pull)

- 2Mbps (Open Drain)

- Power Supply Range:

- A Port and VCCA: 1.65 V to 3.6 V

- B Port and VCCB: 2.3 V to 5.5 V

- VCCA ≤ VCCB

- Pull Up Resistors are Integrated in A Port and B Port

- No Power-Supply Sequencing Required: Either VCCA or VCCB Can be Ramped First

- Support Ultra-Low Power Consumption Mode with OE Pin is Low Voltage Level

- I/O Pin ESD:

- A Port: 2.5 kV (HBM)

- B Port: 6 kV (HBM)

- Latch -Up Performance Exceeds ±200mA Under JESD 78 Standard

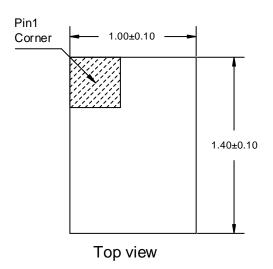

- DFN 1.4mm×1.0mm×0.37mm-8L Package

## GENERAL DESCRIPTION

AW39102 is a 2-bit high-performance voltage-level translator without direction control signal, which is a non-inverting converter and can be used to convert digital signal with mixed-voltage systems. It needs two separate power supply rails, with the A ports tracks the  $V_{\rm CCA}$  ranging from 1.65 V to 3.6 V, and the B ports tracks the  $V_{\rm CCB}$  ranging from 2.3 V to 5.5 V. This makes the chip has capabilities of support both lower and higher logic signal levels translation between any of the 1.8 V, 2.5 V, 3.3 V, and 5 V voltage nodes.

If the voltage level of output-enable (OE) pin is low, the chip works in the high-impedance state, which costs ultra-low power-supply quiescent current. And the OE input circuit is supplied by VCCA. Meanwhile, OE is recommended to be tied to GND through a pull-down resistor to ensure the high-impedance state during power up or power down.

No power supply sequencing requirements means either VCCA or VCCB can be powered up first, and OE should be enabled after both VCCA and VCCB are established.

#### **APPLICATIONS**

- I<sup>2</sup>C / SMBus

- UART

- GPIO

- Handheld Devices Interface

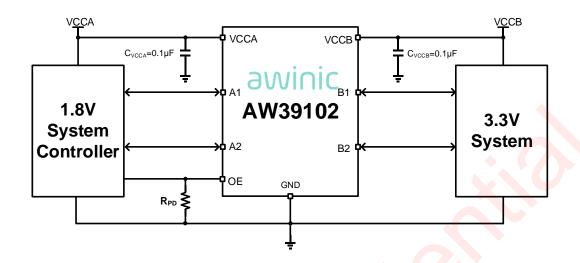

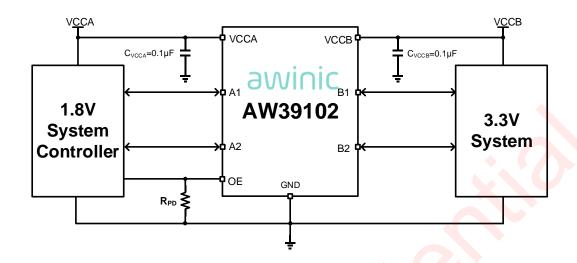

## **APPLICATION CIRCUIT**

Typical Application Circuit of AW39102 Figure 1

All trademarks are the property of their respective owners.

## **PIN CONFIGURATION AND TOP MARK**

#### AW39102DNR PIN Configuration (Top View)

#### AW39102DNR Marking (Top View)

X5G - AW39102DNR XX - Production Tracing Code

Figure 2 Pin Configuration and Top Mark

#### **PIN DEFINITION**

| Pin No. | Pin Name | Description                                                |

|---------|----------|------------------------------------------------------------|

| 1       | VCCA     | A-port supply voltage. 1.65 V ≤ VCCA ≤ 3.6 V, VCCA ≤ VCCB. |

| 2       | A1       | Input/output A1.                                           |

| 3       | A2       | Input/output A2.                                           |

| 4       | GND      | Ground.                                                    |

| 5       | OE       | Output enable.                                             |

| 6       | B2       | Input/output B2.                                           |

| 7       | B1       | Input/output B1.                                           |

| 8       | VCCB     | B-port supply voltage. 2.3 V ≤ VCCB ≤ 5.5 V.               |

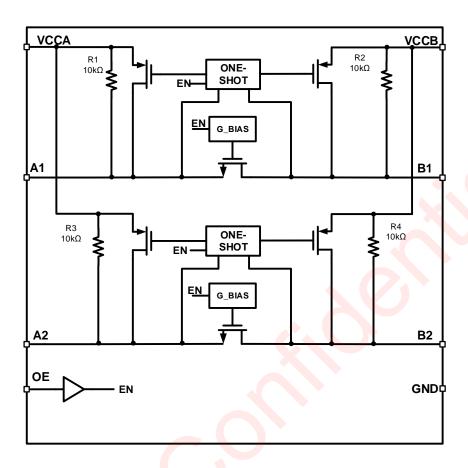

## **FUNCTIONAL BLOCK DIAGRAM**

Figure 3 AW39102 Function Block

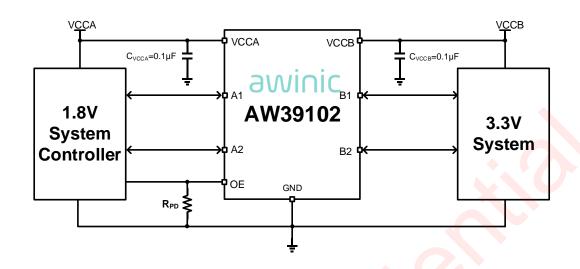

## **TYPICAL APPLICATION CIRCUITS**

Figure 4 AW39102 Application Circuit

#### **ORDERING INFORMATION**

| Part Number | Temperatur<br>e | Package                | Markin<br>g | Moisture<br>Sensitivity<br>Level | Environmenta I Information | Delivery<br>Form             |

|-------------|-----------------|------------------------|-------------|----------------------------------|----------------------------|------------------------------|

| AW39102DNR  | -40°C∼85°C      | DFN 1.4mm×1.0mm-<br>8L | X5G         | MSL1                             | ROHS+HF                    | 3000 units/<br>Tape and Reel |

## **ABSOLUTE MAXIMUM RATINGS**(NOTE1)

| PARAMETERS                                            | MIN    | MAX  | UNIT |    |

|-------------------------------------------------------|--------|------|------|----|

| Supply voltage range V <sub>CCA</sub> (NOTE2          | )      | -0.5 | 5    | V  |

| Supply voltage range V <sub>CCB</sub> (NOTE:          | 2)     | -0.5 | 6.5  | V  |

| Input voltage range, V <sub>I</sub> (NOTE2)           | A port | -0.5 | 5    | V  |

|                                                       | B port | -0.5 | 6.5  | V  |

| Output voltage range in high or low state, Vo (NOTE2) | A port | -0.5 | 5    | V  |

| Output voltage range in high or low state, voltage    | B port | -0.5 | 6.5  | V  |

| Operating free-air temperature rai                    | nge    | -40  | 85   | °C |

| Operating junction temperature                        | -40    | 125  | °C   |    |

| Storage temperature T <sub>STG</sub>                  | -65    | 150  | °C   |    |

| Lead temperature (Soldering 10 sec                    | conds) |      | 260  | °C |

NOTE1: Conditions out of those ranges listed in "absolute maximum ratings" may cause permanent damages to the device. In spite of the limits above, functional operation conditions of the device should within the ranges listed in "recommended operating conditions". Exposure to absolute-maximum-rated conditions for prolonged periods may affect device reliability.

NOTE2: With respect to GND

#### **ESD RATING AND LATCH UP**

| PARAMETERS                             | VALUE                 | UNIT |

|----------------------------------------|-----------------------|------|

| B Port HBM (Human Body Model) (NOTE 3) | ±6                    | kV   |

| Other PINS HBM (Human Body Model)      | ±2.5                  | kV   |

| CDM(NOTE 4)                            | ±1.5                  | kV   |

| Latch-Up(NOTE 5)                       | +IT: 200<br>-IT: -200 | mA   |

NOTE3: The human body model is a 100pF capacitor discharged through a 1.5kΩ resistor into each pin. Test

method: ESDA/JEDEC JS-001-2017

NOTE4: Test method: ESDA/JEDEC JS-002-2014

NOTE5: Test method: JESD78E

## **RECOMMENDED OPERATING CONDITIONS**

VCCI is the VCC associated with the input port

| PAF             | RAMETERS                           | CON                        | DITIONS                                                     | MIN                   | MAX                                             | UNIT     |

|-----------------|------------------------------------|----------------------------|-------------------------------------------------------------|-----------------------|-------------------------------------------------|----------|

| Vcca            | Supply voltage for A port          |                            |                                                             | 1.65                  | 3.6                                             | V        |

| Vccв            | Supply voltage for B port          |                            |                                                             | 2.3                   | 5.5                                             | V        |

|                 |                                    | A-port                     | V <sub>CCA</sub> =1.65V~3.6V<br>V <sub>CCB</sub> =2.3V~5.5V | V <sub>CCI</sub> -0.4 | V <sub>CCI</sub>                                | V        |

| V <sub>IH</sub> | High-level input voltage           | B-port                     | V <sub>CCA</sub> =1.65V~3.6V<br>V <sub>CCB</sub> =2.3V~5.5V | V <sub>CCI</sub> -0.4 | V <sub>CCI</sub>                                | V        |

|                 |                                    | OE input                   | V <sub>CCA</sub> =1.65V~3.6V<br>V <sub>CCB</sub> =2.3V~5.5V | Vcca×0.65             | 5.5                                             | V        |

|                 |                                    | A-port                     | V <sub>CCA</sub> =1.65V~3.6V<br>V <sub>CCB</sub> =2.3V~5.5V | 0                     | 0.4-IoL×RNPASS (NOTE6)                          | V        |

| VIL             | Low-level input voltage            | B-port                     | V <sub>CCA</sub> =1.65V~3.6V<br>V <sub>CCB</sub> =2.3V~5.5V | 0                     | 0.4-I <sub>OL</sub> ×R <sub>NPASS</sub> (NOTE6) | V        |

|                 |                                    | OE input                   | V <sub>CCA</sub> =1.65V~3.6V<br>V <sub>CCB</sub> =2.3V~5.5V | 0                     | V <sub>CCA</sub> ×0.35                          | <b>V</b> |

|                 |                                    | A-port (NOTE 7)            | V <sub>CCA</sub> =1.65V~3.6V<br>V <sub>CCB</sub> =2.3V~5.5V |                       | 10                                              | ns/V     |

| Δt/ΔV           | Input transition rise or fall rate | B-port (NOTE7)             | V <sub>CCA</sub> =1.65V~3.6V<br>V <sub>CCB</sub> =2.3V~5.5V |                       | 10                                              | ns/V     |

|                 |                                    | Control input              | V <sub>CCA</sub> =1.65V~3.6V<br>V <sub>CCB</sub> =2.3V~5.5V |                       | 10                                              | ns/V     |

| T <sub>A</sub>  | Operating junction                 | temperature T <sub>A</sub> |                                                             | -40                   | 85                                              | °C       |

NOTE6: I<sub>OL</sub> is the current from external resistor to output port, R<sub>NPASS</sub> is equal internal resistor of NMOSFET between A port and B port.

NOTE7: The parameter is defined for push-pull driving.

#### THERMAL INFORMATION

| PARAMETERS                                             | VALUE | UNIT  |

|--------------------------------------------------------|-------|-------|

| Junction-to-ambient thermal resistance θ <sub>JA</sub> | 246   | °C /W |

## **ELECTRICAL CHARACTERISTICS**

#### **DC Electrical Characteristics**

Operating under recommended conditions, VCCA ≤ VCCB, T<sub>A</sub>=25°C for typical values (unless otherwise noted)

| P                | ARAMETER                                          | TEST CONDITION                                                            | V <sub>CCA</sub> (V) | V <sub>CCB</sub> (V) | MIN                    | TYP | MAX | UNIT |

|------------------|---------------------------------------------------|---------------------------------------------------------------------------|----------------------|----------------------|------------------------|-----|-----|------|

| Vона             | Port A output high voltage                        | I <sub>OH</sub> = -20μA<br>V <sub>IA</sub> ≥V <sub>CCA</sub> -0.4V        | 1.65~3.6             | 2.3~5.5              | V <sub>CCA</sub> ×0.67 |     |     | V    |

| Vola             | Port A output low voltage                         | I <sub>OL</sub> =1mA V <sub>IA</sub> ≤0.15V                               | 1.65~3.6             | 2.3~5.5              |                        |     | 0.4 | V    |

| V <sub>OHB</sub> | Port B output high voltage                        | I <sub>OH</sub> = -20μA<br>V <sub>IB</sub> ≥V <sub>CCB</sub> -0.4V        | 1.65~3.6             | 2.3~5.5              | V <sub>CCB</sub> ×0.67 |     |     | V    |

| Volb             | Port B output low voltage                         | I <sub>OL</sub> =1mA V <sub>IB</sub> ≤0.15V                               | 1.65~3.6             | 2.3~5.5              |                        |     | 0.4 | V    |

| I.               | OE input                                          | V <sub>I</sub> =V <sub>CCI</sub> or GND,<br>T <sub>A</sub> =25°C          | 1.65~3.6             | 2.3~5.5              | -1                     |     | 1   | μA   |

| I <sub>I</sub>   | leakage current                                   | V <sub>I</sub> =V <sub>CCI</sub> or GND,<br>T <sub>A</sub> =-40°C to 85°C | 1.65~3.6             | 2.3~5.5              | -2                     |     | 2   | μA   |

|                  | A or B port output current in                     | OE=V <sub>IL</sub><br>T <sub>A</sub> =25°C                                | 1.65~3.6             | 2.3~5.5              | -1                     |     | 1   | μΑ   |

| loz              | high impedance state                              | OE=V <sub>IL</sub><br>T <sub>A</sub> =-40°C to 85°C                       | 1.65~3.6             | 2.3~5.5              | -2                     |     | 2   | μΑ   |

|                  |                                                   |                                                                           | 1.65~3.6             | 2.3~5.5              |                        |     | 1   | μΑ   |

| I <sub>CCA</sub> | VCCA supply current                               | V <sub>1</sub> =V <sub>0</sub> =Open<br>I <sub>0</sub> =0                 | 3.6                  | 0                    |                        |     | 1   | μΑ   |

|                  |                                                   | T <sub>A</sub> =-40°C to 85°C                                             | 0                    | 5.5                  |                        |     | -1  | μΑ   |

|                  |                                                   | V V 0707                                                                  | 1.65~3.6             | 2.3~5.5              |                        |     | 8   | μΑ   |

| Іссв             | VCCB supply current                               | V <sub>I</sub> =V <sub>O</sub> =Open<br>I <sub>O</sub> =0                 | 3.6                  | 0                    |                        |     | -1  | μΑ   |

|                  |                                                   | T <sub>A</sub> =-40°C to 85°C                                             | 0                    | 5.5                  |                        |     | 1   | μΑ   |

| ICCB+<br>ICCA    | Combined supply current                           | V <sub>I</sub> =V <sub>O</sub> =Open<br>I <sub>O</sub> =0                 | 1.65~3.6             | 2.3~5.5              |                        |     | 9   | μΑ   |

| R <sub>PU</sub>  | Resistor pull-up value                            | T <sub>A</sub> =25°C                                                      | 1.65~3.6             | 2.3~5.5              | 8                      | 10  | 12  | kΩ   |

| RNPASS           | The resistor of NMOSFET between A port and B port | OE=V <sub>IH</sub><br>T <sub>A</sub> =25°C                                | 1.8                  | 3.3                  |                        | 28  |     | Ω    |

## Timing Requirements (NOTE1)

Output load: C<sub>L</sub>=15pF, push-pull driver, and T<sub>A</sub>=-40°C to 85°C.

| PARAMETER                                                  |                | TEST CONDITION              | MIN | MAX | UNIT |

|------------------------------------------------------------|----------------|-----------------------------|-----|-----|------|

| $V_{CCA}$ =1.8V±0.15V / 2.5V±0.2V / $V_{CCA}$ =3.3V ± 0.3V |                |                             |     |     |      |

|                                                            |                | V <sub>CCB</sub> =2.5V±0.2V |     | 21  |      |

| Data Rate                                                  |                | V <sub>CCB</sub> =3.3V±0.3V |     | 24  | Mbps |

|                                                            |                | V <sub>CCB</sub> =5V±0.5V   |     | 24  |      |

| t <sub>w</sub>                                             | Pulse Duration | V <sub>CCB</sub> =2.5V±0.2V | 45  |     | ns   |

| PAF                       | RAMETER               | TEST CONDITION              | MIN | MAX | UNIT |

|---------------------------|-----------------------|-----------------------------|-----|-----|------|

| V <sub>CCA</sub> =1.8V±0. | 15V / 2.5V±0.2V / Vcc | \=3.3V±0.3V                 |     |     |      |

|                           |                       | V <sub>CCB</sub> =3.3V±0.3V | 40  |     |      |

|                           |                       | V <sub>CCB</sub> =5V±0.5V   | 40  |     |      |

NOTE1: The parameter's variation is guaranteed by design, not production tested.

## Switch Characteristics(NOTE2)

Output load: C<sub>L</sub>=15pF, T<sub>A</sub>=25°C for typical values (unless otherwise noted), V<sub>CCA</sub>=1.8V

| DADAMETED                      | TEST CONDITION  |                | V <sub>CCB</sub> : | =2.5V | V <sub>CCB</sub> =3.3V |      | V <sub>CCB</sub> =5V |      | UNIT |

|--------------------------------|-----------------|----------------|--------------------|-------|------------------------|------|----------------------|------|------|

| PARAMETER                      | TEST            | TEST CONDITION |                    | MAX   | MIN                    | MAX  | MIN                  | MAX  | UNII |

| t <sub>PHL</sub> (NOTE3)       | A-B             | Push-pull      |                    | 11    |                        | 7.0  |                      | 5.0  | 20   |

| LPHL(NOTES)                    | A-D             | Open-drain     | 2.3                | 8.8   | 2.4                    | 9.6  | 2.6                  | 10   | ns   |

| t <sub>PLH</sub> (NOTE3)       | A-B             | Push-pull      |                    | 7.5   |                        | 6.7  |                      | 5.7  | 20   |

| LPLH(110723)                   | A-D             | Open-drain     | 45                 | 260   | 36                     | 208  | 27                   | 198  | ns   |

| t <sub>PHL</sub> (NOTE3)       | B-A             | Push-pull      |                    | 9.0   |                        | 5.5  |                      | 5.0  | 20   |

| LPHL(NOTES)                    | D-A             | Open-drain     | 1.9                | 5.3   | 1.1                    | 4.4  | 1.2                  | 4    | ns   |

| t <sub>PLH</sub> (NOTE3)       | (NOTE2)         | Push-pull      |                    | 7.4   |                        | 5.8  |                      | 4.1  | 20   |

| IPLH(NOTES)                    | B-A             | Open-drain     | 45                 | 175   | 36                     | 140  | 27                   | 102  | ns   |

| t <sub>en</sub><br>Enable time | OE-A or B       |                |                    | 45    |                        | 35   |                      | 30   | ns   |

| t <sub>dis</sub> disable time  | OE-A or B       | . (1           |                    | 200   |                        | 200  |                      | 200  | ns   |

| t <sub>rA</sub>                | A port          | Push-pull      | 3.2                | 9.5   | 2.3                    | 9.3  | 2                    | 7.6  |      |

| Input rise time                | rise time       | Open-drain     | 38                 | 165   | 30                     | 132  | 22                   | 95   | ns   |

| t <sub>rB</sub>                | B port          | Push-pull      | 4                  | 10.8  | 2.7                    | 9.1  | 2.7                  | 7.6  |      |

| Input rise time                | rise time       | Open-drain     | 34                 | 145   | 23                     | 106  | 10                   | 58   | ns   |

| t <sub>fA</sub>                | A port          | Push-pull      | 2                  | 5.9   | 1.9                    | 6    | 1.7                  | 13.3 |      |

| Input fall time                | fall time       | Open-drain     | 4.4                | 6.9   | 4.3                    | 6.4  | 4.2                  | 6.1  | ns   |

| t <sub>fB</sub>                | B port          | Push-pull      | 2.9                | 13.8  | 2.8                    | 16.2 | 2.8                  | 16.2 |      |

| Input fall time                | fall time       | Open-drain     | 6.9                | 13.8  | 7.5                    | 16.2 | 7                    | 16.2 | ns   |

| tsk<br>Skew time               | Channel to skew | channel        |                    | 0.7   |                        | 0.7  |                      | 0.7  | ns   |

Output load: C<sub>L</sub>=15pF, T<sub>A</sub>=25°C for typical values (unless otherwise noted), V<sub>CCA</sub>=2.5V

| DADAMETED                      | TEST CONDITION             |            | V <sub>CCB</sub> : | =2.5V | V <sub>CCB</sub> =3.3V |     | V <sub>CCB</sub> =5V |      | LINIT |

|--------------------------------|----------------------------|------------|--------------------|-------|------------------------|-----|----------------------|------|-------|

| PARAMETER                      | IESIC                      | ONDITION   | MIN                | MAX   | MIN                    | MAX | MIN                  | MAX  | UNIT  |

| t <sub>PHL</sub> (NOTE3)       | A-B                        | Push-pull  |                    | 3.2   |                        | 3.7 |                      | 3.8  | 50    |

| LPHL(110725)                   | A-D                        | Open-drain | 1.7                | 6.3   | 2                      | 6   | 2.1                  | 5.8  | ns    |

| t <sub>PLH</sub> (NOTE3)       | A-B                        | Push-pull  |                    | 3.5   |                        | 4.1 |                      | 4.4  | 20    |

| LPLH(110723)                   | A-D                        | Open-drain | 45                 | 250   | 36                     | 206 | 27                   | 190  | ns    |

| t <sub>PHL</sub> (NOTE3)       | B-A                        | Push-pull  |                    | 3     |                        | 3.6 |                      | 4.3  | 20    |

| TPHL(NOTES)                    | B-A                        | Open-drain | 1.8                | 4.7   | 2.6                    | 4.2 | 1.2                  | 4    | ns    |

| t <sub>PLH</sub> (NOTE3)       | PLH <sup>(NOTE3)</sup> B-A | Push-pull  |                    | 2.5   |                        | 1.6 |                      | 1    |       |

| IPLH(NOTES)                    | B-A                        | Open-drain | 44                 | 170   | 37                     | 140 | 27                   | 102  | ns    |

| t <sub>en</sub><br>Enable time | OE-A or B                  |            |                    |       |                        | 35  |                      | 30   | ns    |

| t <sub>dis</sub> disable time  | OE-A or B                  |            |                    |       |                        | 200 |                      | 200  | ns    |

| trA                            | A port                     | Push-pull  | 2.8                | 7.4   | 2.6                    | 6.6 | 1.8                  | 5.6  |       |

| Input rise time                | rise time                  | Open-drain | 38                 | 150   | 28                     | 121 | 24                   | 89   | ns    |

| t <sub>rB</sub>                | B port                     | Push-pull  | 3.2                | 8.3   | 2.9                    | 7.2 | 2.4                  | 6.1  |       |

| Input rise time                | rise time                  | Open-drain | 34                 | 151   | 24                     | 112 | 12                   | 64   | ns    |

| t <sub>fA</sub>                | A port                     | Push-pull  | 1.9                | 5.7   | 1.9                    | 5.5 | 1.8                  | 5.3  |       |

| Input fall time                | fall time                  | Open-drain | 4.4                | 6.9   | 4.3                    | 6.4 | 4.2                  | 5.8  | ns    |

| t <sub>fB</sub>                | B port                     | Push-pull  | 2.2                | 7.8   | 2.4                    | 6.7 | 2.6                  | 6.6  |       |

| Input fall time                | fall time                  | Open-drain | 5.1                | 8.8   | 5.4                    | 9.4 | 5.4                  | 10.4 | ns    |

| tsk<br>Skew time               | Channel to skew            | channel    |                    | 0.7   |                        | 0.7 |                      | 0.7  | ns    |

awinic

Output load: C<sub>L</sub>=15pF, T<sub>A</sub>=25°C for typical values (unless otherwise noted), VCCA=3.3V

| PARAMETER                                | TEST (     | CONDITION    | V <sub>CCB</sub> = | =3.3V | Vcc | :B=5V | UNIT |

|------------------------------------------|------------|--------------|--------------------|-------|-----|-------|------|

| TAKAWETEK                                | 1231 (     | CHEITICH     | MIN                | MAX   | MIN | MAX   |      |

| t <sub>PHL</sub> (NOTE3)                 | A-B        | Push-pull    |                    | 2.4   |     | 3.1   | ns   |

| (PHL(*********************************** | A-D        | Open-drain   | 1.3                | 4.2   | 1.4 | 4.6   |      |

| t <sub>PLH</sub> (NOTE3)                 | A-B        | Push-pull    |                    | 4.2   |     | 4.4   | ns   |

| VELIT: /                                 | A-B        | Open-drain   | 36                 | 204   | 27  | 165   |      |

| t <sub>PHL</sub> (NOTE3)                 | B-A        | Push-pull    |                    | 2.5   | •   | 3.3   | ns   |

| (PHL)******                              | D-A        | Open-drain   | 1                  | 124   | 1   | 97    |      |

| t <sub>PLH</sub> (NOTE3)                 | ВА         | Push-pull    |                    | 2.5   |     | 3.3   | ns   |

| t <sub>PLH</sub> (NOTE3) B-A             | B-A        | Open-drain   | 3                  | 139   | 3   | 105   |      |

| t <sub>en</sub><br>Enable time           | OE-A or B  |              |                    |       |     | 30    | ns   |

| t <sub>dis</sub> disable time            | OE-A or B  |              |                    |       |     | 200   | ns   |

| t <sub>rA</sub>                          | A port     | Push-pull    | 2.3                | 5.6   | 1.9 | 4.8   | ns   |

| Input rise time                          | rise time  | Open-drain   | 25                 | 116   | 19  | 85    |      |

| t <sub>rB</sub>                          | B port     | Push-pull    | 2.5                | 6.4   | 2.1 | 7.4   | ns   |

| Input rise time                          | rise time  | Open-drain   | 26                 | 116   | 14  | 72    |      |

| t <sub>fA</sub>                          | A port     | Push-pull    | 2                  | 5.4   | 1.9 | 5     | ns   |

| Input fall time                          | fall time  | Open-drain   | 4.3                | 6.4   | 4.2 | 5.7   |      |

| t <sub>fB</sub>                          | B port     | Push-pull    | 2.3                | 7.4   | 2.4 | 7.6   | ns   |

| Input fall time                          | fall time  | Open-drain   | 5                  | 7.6   | 4.8 | 8.3   |      |

| t <sub>SK</sub><br>Skew time output      | Channel to | channel skew |                    | 0.7   |     | 0.7   | ns   |

NOTE2: The parameters is guaranteed by design, not production tested.

NOTE3: tphl presents propagation delay from high to low, and tplh presents propagation delay from low to high.

#### TYPICAL CHARACTERISTICS

#### **Test Information**

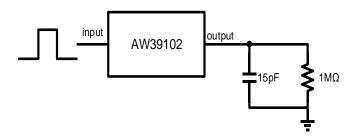

Test Circuit for Date Rate, Pulse Duration, Propagation Delay, Rise Time and Fall Time

Figure 5 Load Circuit of Push-Pull Driver

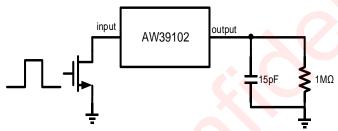

Test Circuit for Date Rate, Pulse Duration, Propagation Delay, Rise Time and Fall Time

Figure 6 Load Circuit of Open-Drain Driver

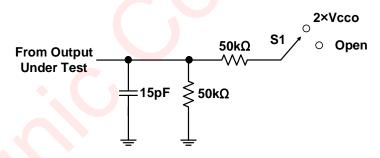

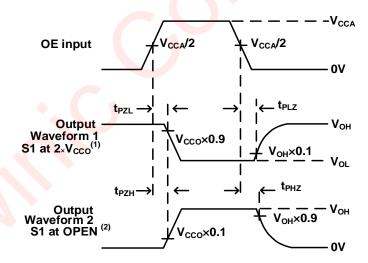

| TEST                                                     | S1                   |

|----------------------------------------------------------|----------------------|

| $t_{PZL}/t_{PLZ}$ $(t_{dis})$                            | 2 × V <sub>cco</sub> |

| t <sub>PHZ</sub> /t <sub>PZH</sub><br>(t <sub>en</sub> ) | Open                 |

- 1. tplz and tphz are the same as tdis.

- 2.  $t_{PZL}$  and  $t_{PZH}$  are the same as  $t_{en}$ .

- 3. VCCI is the VCC associated with the input port.

- 4. VCCO is the VCC associated with the output port.

- 5. The resistance and Capacitance values at output notes above are the total effective values.

Figure 7 Load Circuit for Enable-Time and Disable-Time Measurement

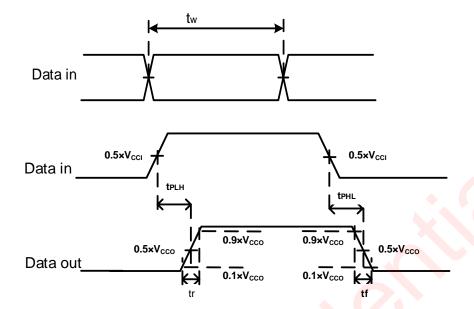

The input pulses should have the following characteristics:

- 1.  $f_{IN} \leq 10MHz$ .

- 2.  $dv/dt \ge 1V/ns$ .

Figure 8 Timing Parameter Definition

- (1) The Waveform 1 is obtained under the condition that the input is low and S1 at 2\*Vcco.

- (2) The Waveform 2 is obtained under the condition that the input and S1 at OPEN.

Figure 9 Enable and Disable Times

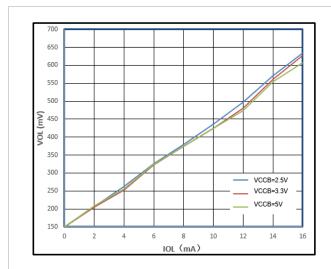

#### Typical Curve T<sub>A</sub>=25°C

V<sub>CCA</sub>=1.8V, OE=1, V<sub>ILA</sub>=0.15V

Figure 10 **Low-Level Output Voltage** vs Low-Level Current

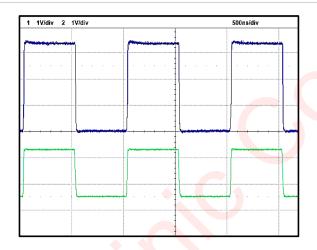

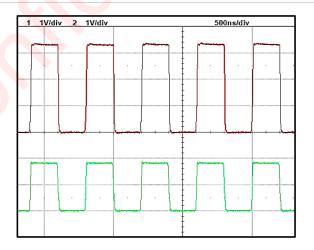

Vcca=1.8V, Vccb=3.3V, OE=1, Push-Pull Driver Signal is translated from A port to B port

Figure 12 Level Translation of a 1MHz Signal

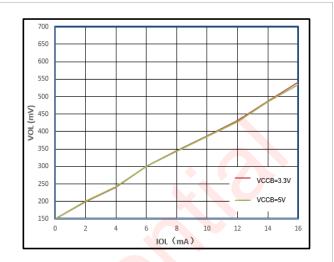

V<sub>CCA</sub>=3.3V, OE=1, V<sub>ILA</sub>=0.15V

Figure 11 Low-Level Output Voltage vs Low-Level Current

VCCA=1.8V, VCCB=3.3V, OE=1, Push-Pull Driver Signal is translated from A port to B port

Figure 13 Level Translation of a 2.5MHz Signal

#### **DETAILED FUNCTIONAL DESCRIPTION**

AW39102 is a 2-bit high-performance voltage-level translator without direction control signal, which is a non-inverting converter and can be used to convert digital signal with mixed-voltage systems. Port A can support I/O voltages from 1.65 V to 3.6 V, while Port B is able to support I/O voltage range from 2.3 V to 5.5 V. The chip uses a transmission gate architecture with an rising edge rate accelerator (one-shot), to increase overall data rate. Also,  $10k\Omega$  pull-up resistors are integrated in the chip, which ensures the chip not only supports push-pull applications but also can be used in open-drain applications directly.

#### **One-shot Accelerator**

The One-Shot rising edge accelerator circuit speeds up the rising edge to help increasing the chip's data rate. Once the chip has detected the rising edge of the input signal from low to high, the one-shot circuit generates a pulse signal of approximately 25ns, which enables the internal pull-up PMOS transistor between power supply and output, thereby accelerating the output port from low to high. During this acceleration phase, the output resistance of the driver is reduced from  $10k\Omega$  to approximately  $60\Omega$ . While detecting the output has been turned up, the one-shot pulse signal is finished and pull-up PMOS transistor is quickly turned off. This architecture reduces the average dynamic power consumption of the chip while allowing it to meet different drive requirements.

#### **Gate Bias**

For the bidirectional voltage translator AW39102, a NMOS switch transistor is used between the input and output. When translating high level, the NMOS transistor is turned off, and the input and output terminals are isolated so that they do not impact each other. When the low level is translated, the NMOS switch transistor is fully turned on, so that the output terminal can be quickly pulled down to the low voltage level. Therefore, the gate bias voltage of the NMOS switch transistor is set to a fixed value about VCCA+VTH. It is also because of this architecture that VCCA≤VCCB needs to be guaranteed in the applications.

#### **Enable Control**

The AW39102's OE pin can disable the chip by setting OE to low voltage level, allowing all I/O to operate in the Hi-Z state. The disable time (tdis) represents the delay time from OE going low to the chip turns to Hi-Z state. In the Hi-Z state, the chip consumes ultra-low current. And the enable time (ten) indicates the delay from OE going high to the chip working in translation state. Meanwhile, OE is recommended to be tied to GND through a pull-down resistor to ensure the high-impedance state during power up or power down. The minimum value of the resistor is determined by the current-sourcing capability of the driver.

#### Input Driver

The rising edge time of the signal ( $t_{rA}$ ,  $t_{rB}$ ) and propagation delay from low to high ( $t_{PLH}$ ) are determined by the rising edge rate of the input signal, the ONE-SHOT accelerator's pull-up capability, and the capacitive load of the port. The falling edge time of the signal ( $t_{rA}$ ,  $t_{rB}$ ) depends on the falling edge rate of the input signal, the output impedance of the external driver, and the capacitive load on the data line. Similarly,  $t_{PHL}$  and the maximum data rate also depend on the output impedance of the external driver. So, the test conditions for  $t_{rA}$ ,  $t_{rB}$ ,  $t_{rA}$ ,  $t_{rB}$ ,  $t_{rB}$ ,  $t_{rBL}$ ,  $t_$

#### **Output Load**

It is recommended that a PCB layout with short PCB layout length:

Dec. 2019 V1.2

- 1. Avoid excessive capacitive load triggers ONE-SHOT circuit falsely;

- 2. It can ensure that the round trip delay of any reflection is less than a single ONE-SHOT duration;

- 3. Improve signal integrity.

awinic

Meanwhile, the pulse width of the ONE-SHOT circuit is approximately 25 ns, which determines the maximum output load capacitance that the chip can drive. For very heavy output capacitive loads, the one-shot accelerator will time-out before the output is fully pulled to high level, at which case the signal transmission will be distorted. So the ONE-SHOT duration design requires a trade-off between dynamic power consumption, capacitive load driving capability and maximum data rate. The signal tw at the maximum translation rate should be greater than the maximum pulse width of the ONE-SHOT circuit, and the delay caused by the output capacitive load should be less than the maximum pulse width of the ONE-SHOT circuit.

#### **APPLICATION INFORMATION**

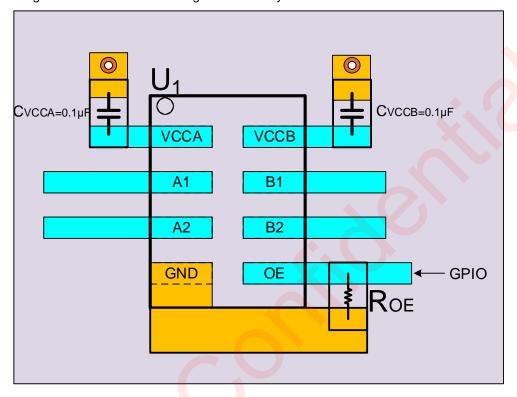

Figure 14 AW39102 Application Circuit

AW39102 is a 2-bit voltage-level translator without direction control signal, which is suitable for interfacing devices or systems operating at different interface voltages with one another. Port A can supports I/O voltages from 1.65 V to 3.6 V, while Port B is able to support I/O voltage range from 2.3 V to 5.5 V. Also,  $10k\Omega$  pull-up resistors are integrated in the chip, which ensures the chip not only supports push-pull applications but also can be used in open-drain applications directly.

#### **VCC Capacitor Selection**

The device is a 2-bit high-performance voltage-level translator that requires adequate power supply decoupling. Place a low equivalent-series-resistance (ESR) ceramic capacitor, recommend 0.1µF or larger than 0.1µF.

#### **RPD Selection**

Drive OE pin HIGH to enable the device. If the voltage level of OE pin is low, the device works in High-impedance mode. OE pin is recommended to be tied to GND through a pull-down resistor to ensure the high-impedance state during power up or power down. OE pin is high impedance without internal pull down resistor, customer can choose the resistor value based on the source drive capability and current consumption.

#### **PCB LAYOUT CONSIDERATION**

To make full use of the performance of AW39102, the guidelines below should be followed.

- 1. Cvcca and Cvccb should be placed on the top layer as close as possible to the VCCA and VCCB pin.

- 2. The trace of signals should be short enough to avoid any reflection when transmitted.

Figure 15 AW39102 Layout Example

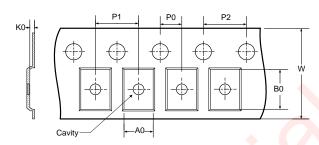

#### TAPE AND REEL INFORMATION

# **REEL DIMENSIONS** 0 D1

#### TAPE DIMENSIONS

- A0: Dimension designed to accommodate the component width B0: Dimension designed to accommodate the component length

- K0: Dimension designed to accommodate the component thickness

- W: Overall width of the carrier tape

P0: Pitch between successive cavity centers and sprocket hole

- P1: Pitch between successive cavity centers

- P2: Pitch between sprocket hole

- D1: Reel Diameter

- D0: Reel Width

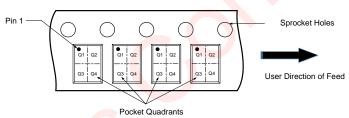

#### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### All Dimensions are nominal

| D1<br>(mm) | D0<br>(mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P0<br>(mm) | P1<br>(mm) | P2<br>(mm) | W<br>(mm) | Pin1 Quadrant |

|------------|------------|------------|------------|------------|------------|------------|------------|-----------|---------------|

| 180        | 9.5        | 1.15       | 1.6        | 0.5        | 2          | 4          | 4          | 8         | Q1            |

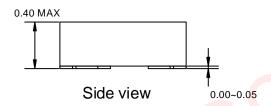

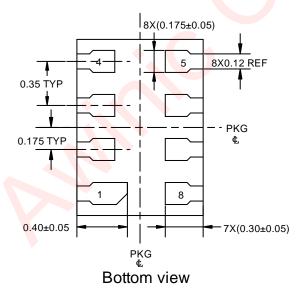

## PACKAGE DESCRIPTION(POD)

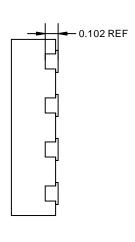

Side view

Unit: mm

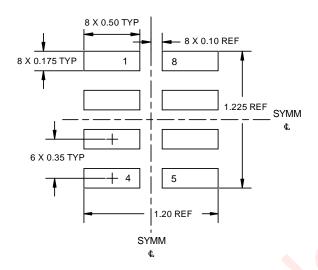

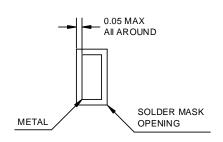

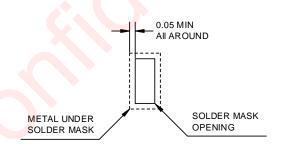

## **LAND PATTERN DATA**

NON-SOLDER MASK DEFINED

SOLDER MASK DEFINED

Unit: mm

## **REVISION HISTORY**

| Vision | Date      | Change Record                                                 |

|--------|-----------|---------------------------------------------------------------|

| V1.0   | Apr. 2019 | Official Released                                             |

| V1.1   | May. 2019 | Update waveform                                               |

| V1.2   | Dec. 2019 | Update the Definition of V <sub>IL</sub> and t <sub>dis</sub> |

#### **DISCLAIMER**

Information in this document is believed to be accurate and reliable. However, Shanghai AWINIC Technology Co., Ltd (AWINIC Technology) does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information.

AWINIC Technology reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. Customers shall obtain the latest relevant information before placing orders and shall verify that such information is current and complete. This document supersedes and replaces all information supplied prior to the publication hereof.

AWINIC Technology products are not designed, authorized or warranted to be suitable for use in medical, military, aircraft, space or life support equipment, nor in applications where failure or malfunction of an AWINIC Technology product can reasonably be expected to result in personal injury, death or severe property or environmental damage. AWINIC Technology accepts no liability for inclusion and/or use of AWINIC Technology products in such equipment or applications and therefore such inclusion and/or use is at the customer's own risk.

Applications that are described herein for any of these products are for illustrative purposes only. AWINIC Technology makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

All products are sold subject to the general terms and conditions of commercial sale supplied at the time of order acknowledgement.

Nothing in this document may be interpreted or construed as an offer to sell products that is open for acceptance or the grant, conveyance or implication of any license under any copyrights, patents or other industrial or intellectual property rights.

Reproduction of AWINIC information in AWINIC data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. AWINIC is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of AWINIC components or services with statements different from or beyond the parameters stated by AWINIC for that component or service voids all express and any implied warranties for the associated AWINIC component or service and is an unfair and deceptive business practice. AWINIC is not responsible or liable for any such statements.

## 单击下面可查看定价,库存,交付和生命周期等信息

## >>AWINIC(艾为)