## 4/5 Cells Li-Ion and Li-Polymer Battery Protector

### 1. Features

- High Accuracy Voltage Detection

- Charge over voltage protection

Vov: 3.2V 4.4V(Step: 25mV)

- Charge over voltage protection accuracy: ±15mV

- . Release hysteresis voltage: 0 400mV

- Discharge under voltage Protection

V<sub>UV</sub>: 2.0V 3.6V (Step: 100mV)

- Discharge under voltage protection accuracy: ±50mV

- Discharge under voltage protection release hysteresis voltage: 0 - 1.6V

- Discharge Over Current Detection:

- Discharge over current 1 protection voltage

V<sub>DOC1</sub>: 0.025V 0.400V (Step: 12.5mV)

- Discharge over current 1 protection voltage accuracy: ±10mV

- Discharge over current 1 protection voltage

V<sub>DOC2</sub>: 2×V<sub>DOC1</sub> (Step: 25mV)

- Discharge over current 2 protection voltage accuracy: ±15mV

- Short Protection:

- Short protection voltage

Vsc: 4×V<sub>DOC1</sub> (Step: 50mV)

- . Short protection voltage accuracy: ±15mV

- Charge Over Current Protection:

- Charge over current protection voltage V<sub>COC</sub>:

10mV 50mV (Step: 10mV)

- Charge over current protection voltage accuracy:

10mV: ±5mV, 20mV 50mV: ±10mV

- Open Wire Detection

- Battery Cell Balance:

- . Balance operation voltage threshold:

- . 3.2V 4.375V (25mV step)

- Balance operation voltage accuracy: ±25mV

- Temperature Protection:

- Charging high temperature protection : 50°C

Protection accuracy: ±4°C(Max.)

- Charging low temperature protection : -5°C

Protection accuracy: ±4°C (Max.)

- Discharging high temperature protection: 70°C

Protection accuracy: ±4°C (Max.)

- External capacitor to set over discharge voltage protection delay time, over discharge current 1 protection delay time and over discharge current 2 protection delay time

- Fixed over charge voltage, over charge current protection delay time, short protection delay time and temperature protection delay time

- Low Power Consumption

- Normal operation mode current: 20µA (Max)

- Sleep mode current: 3µA (Max)

- Operation Temperature Range: -40°C ~ 85°C

- Operation Voltage Range: 3V ~ 40V

- Package: 20-pin TSSOP20

- SEL pin to configure 4/5 cells application

# 2. General Description

- SIT8995 integrates high accuracy voltage detection circuits and time delay circuits to monitor battery cell voltage, current and temperature and to protect Li-lon and Li-Polymer battery package safety. SIT8995 has function with charging from 0V which can increase battery pack service life.

- SIT8995 has three operation mode: normal mode, sleep mode and shutdown mode.

SIT8995 enters sleep mode to reduce system power consumption when any battery cell is in low battery status.

TMÍ SUNTO

www.toll-semi.com

# 3. Typical Application Circuits

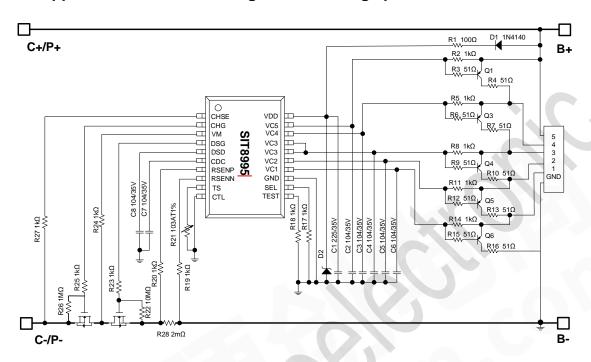

### 5 cells application with same charge and discharge port

Figure 1. SIT8995 Typical Application Circuits (5 cells application with same charge and discharge port)

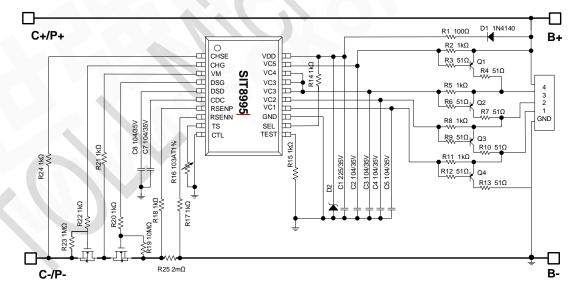

### 4 cells application with same charge and discharge port

Figure 2. SIT8995 Typical Application Circuits (4 cells application with same charge and discharge port)

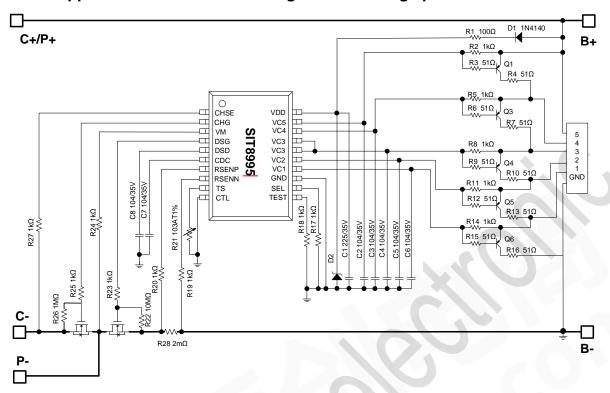

## 5 cells application with different charge and discharge port

Figure 3. SIT8995 Typical Application Circuits (5 cells application with different charge and discharge port)

# 4. Absolute Maximum Ratings

| Parameters            | Symbol           | Max                                      | Min                  | Unit |  |

|-----------------------|------------------|------------------------------------------|----------------------|------|--|

| VDD input voltage     | $V_{DD}$         | -0.3                                     | 40                   | V    |  |

| High voltage port     | DSG/VC1-VC5/SEL  | GND-0.3                                  | V <sub>DD</sub> +0.3 |      |  |

| High voltage port     | VDD/VM/CHG/CHSE  | V <sub>DD</sub> -40 V <sub>DD</sub> +0.3 |                      | V    |  |

| Low voltage port      | CDC/DSD/TS/TEST/ | GND-0.3                                  | 5.5                  | \/   |  |

| Low voitage port      | CTL/RSNSP/RSNSN  | GIND-0.3                                 | 5.5                  | V    |  |

| Operation temperature | T <sub>OP</sub>  | -40                                      | 85                   | °C   |  |

| Storage temperature   | T <sub>STR</sub> | -40                                      | 125                  | °C   |  |

Note 1: Application cannot exceed the maximum ratings in case damage the device.

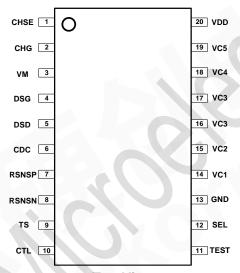

# 5. Pin Map

**Top View**

Package: TSSOP20

## 6. Order Information

| Part<br>Number  | V <sub>OVP</sub><br>(V) | V <sub>OVR</sub> (V) | V <sub>BL</sub><br>(V) | V <sub>UVP</sub><br>(V) | V <sub>UVR</sub><br>(V) | V <sub>DOCP</sub> (V) | V <sub>COCP</sub> (V) | Load<br>Lock | Open Wire<br>Detection | Quantity |

|-----------------|-------------------------|----------------------|------------------------|-------------------------|-------------------------|-----------------------|-----------------------|--------------|------------------------|----------|

| SIT8995A        | 4.250                   | 4.150                | 4.200                  | 2.700                   | 3.000                   | 0.100                 | 0.050                 | Yes          | Yes                    | 3000     |

| SIT8995B        | 3.900                   | 3.600                | 3.850                  | 2.200                   | 2.700                   | 0.100                 | 0.050                 | Yes          | Yes                    | 3000     |

| <u>SIT8995C</u> | 3.850                   | 3.750                | 3.650                  | 2.000                   | 2.500                   | 0.100                 | 0.015                 | Yes          | Yes                    | 3000     |

| SIT8995D        | 3.750                   | 3.550                | 3.515                  | 2.200                   | 2.700                   | 0.100                 | 0.040                 | Yes          | Yes                    | 3000     |

| SIT8995F        | 4.175                   | 4.075                | 4.125                  | 2.700                   | 3.000                   | 0.100                 | 0.040                 | Yes          | Yes                    | 3000     |

| SIT8995G        | 4.225                   | 4.125                | 4.175                  | 2.700                   | 3.000                   | 0.100                 | 0.040                 | Yes          | Yes                    | 3000     |

# 7. Pin Configuration

| Pin | Name  | 1/0 | Function Description                                    |

|-----|-------|-----|---------------------------------------------------------|

| 1   | CHSE  | I   | Charger detection pin                                   |

| 2   | CHG   | 0   | Charging MOSFET control pin                             |

| 3   | VM    | I   | Load detection pin                                      |

| 4   | DSG   | 0   | Discharging MOSFET control pin                          |

| 5   | DSD   | I/O | Discharge delay time capacitor set pin                  |

| 6   | CDC   | I/O | Over discharge current 1/2 delay time capacitor set pin |

| 7   | RSNSP | I   | Positive current sense pin                              |

| 8   | RSNSN | I   | Negative current sense pin                              |

| 9   | TS    | I   | NTC resistor connection pin                             |

| 10  | CTL   | I   | DSG、CHG output control pin                              |

| 11  | TEST  | I   | Test pin                                                |

| 12  | SEL   | I   | Selection pin for 4 or 5 cells                          |

| 13  | GND   |     | Power ground                                            |

| 14  | VC1   | I   | The first battery cell positive connection pin          |

| 15  | VC2   | I   | The second battery cell positive connection pin         |

| 16  | VC3   | 1   | The third battery cell positive connection pin          |

| 17  | VC3   | 1   | The third battery cell positive connection pin          |

| 18  | VC4   |     | The fourth battery cell positive connection pin         |

| 19  | VC5   |     | The highest battery cell positive connection pin        |

| 20  | VDD   |     | Power connection pin                                    |

# 8. ESD Rating

| Parameters | Description                   | Value | Unit |

|------------|-------------------------------|-------|------|

| $V_{ESD}$  | Human Body Model for all pins | ±2000 | V    |

JEDEC specification JS-001

# 9. Electrical CharacteriSITcs

(T<sub>A</sub> = 25°C, unless otherwise noted.)

| Parameters                                                  | Symbol             | Condition                                     | Min       | Тур | Max      | Unit     |

|-------------------------------------------------------------|--------------------|-----------------------------------------------|-----------|-----|----------|----------|

| Charge Over Voltage Protect                                 | tion               |                                               |           |     |          |          |

| Charge over voltage protection voltage                      | Vov                | _                                             | 3.200     |     | 4.400    | V        |

| Charge over voltage protection voltage accuracy             | V <sub>OVA</sub>   | _                                             | -15       |     | 15       | mV       |

| Charge over voltage protection voltage step                 | Vovs               | _                                             |           | 25  | <b>\</b> | mV       |

| Charge over voltage protection release voltage              | V <sub>OVR</sub>   | _                                             | 3.200     |     | 4.400    | V        |

| Charge over voltage protection release voltage accuracy     | V <sub>OVRA</sub>  |                                               | -25       |     | 25       | mV       |

| Charge over voltage protection release voltage step         | V <sub>OVRS</sub>  |                                               |           | 25  |          | mV       |

| Charge over voltage protection delay time                   | Tov                |                                               | 0.5       | 1   | 1.5      | s        |

| Charge over voltage protection release delay time           | T <sub>OVR</sub>   |                                               | 0.5       | 1   | 1.5      | ms       |

| Discharge Under Voltage Pro                                 | otection           |                                               |           |     |          |          |

| Discharge under voltage protection voltage                  | V <sub>UV</sub>    | -                                             | 2.000     |     | 3.600    | V        |

| Discharge under voltage protection voltage accuracy         | V <sub>UVA</sub>   |                                               | -50       |     | 50       | mV       |

| Discharge under voltage protection voltage step             | V <sub>UVS</sub>   | A E                                           |           | 100 |          | mV       |

| Discharge under voltage protection release voltage          | V <sub>UVR</sub>   |                                               | 2.000     |     | 3.700    | V        |

| Discharge under voltage protection release voltage accuracy | Vuvra              |                                               | -50       |     | 50       | mV       |

| Discharge under voltage protection release voltage step     | V <sub>UVRS</sub>  |                                               |           | 100 |          | mV       |

| Discharge under voltage protection delay time               | tuv                | 0.1µF capacitor on DSD pin with ±10% accuracy | 0.5       | 1   | 1.5      | S        |

| Discharge under voltage protection release delay time       | t <sub>UVR</sub>   | 0.1µF capacitor on DSD pin with ±10% accuracy | 50        | 100 | 150      | ms       |

| <b>Charge Over Current Protect</b>                          | ion                | · •                                           |           |     |          |          |

| Charge over voltage protection voltage                      | V <sub>coc</sub>   |                                               | 10        |     | 50       | mV       |

| Charge over voltage protection voltage accuracy             | V <sub>COCA</sub>  | 10mV/step<br>20mV-50mV/step                   | -5<br>-10 |     | 5<br>10  | mV<br>mV |

| Charge over voltage protection voltage step                 | V <sub>cocs</sub>  |                                               |           | 10  |          | mV       |

| Charge over voltage protection delay time                   | tcoc               |                                               | 0.5       | 1   | 1.5      | s        |

| Charge over voltage protection release delay time           | tcocr              |                                               | 50        | 100 | 150      | ms       |

| Discharge Over Current Prot                                 | ection             |                                               | I.        | I.  | 1        | 1        |

| Discharge over current 1 protection voltage                 | V <sub>DOC1</sub>  |                                               | 25        |     | 400      | mV       |

| Discharge over current 1 protection voltage accuracy        | V <sub>DOC1A</sub> |                                               | -10       |     | 10       | mV       |

## 9. Electrical CharacteriSITcs

$(T_A = 25^{\circ}C, unless otherwise noted.)$

| Parameters                                                | Symbol             | Condition                                     | Min | Тур                  | Max   | Unit |

|-----------------------------------------------------------|--------------------|-----------------------------------------------|-----|----------------------|-------|------|

| Discharge over current 1 protection voltage step          | V <sub>DOC1S</sub> |                                               |     | 12.5                 |       | mV   |

| Discharge over current 1 protection delay time            | t <sub>DOC1</sub>  | 0.1µF capacitor on CDC pin with ±10% accuracy | 0.5 | 1                    | 1.5   | s    |

| Discharge over current 2 protection voltage               | V <sub>DOC2</sub>  |                                               |     | 2*V <sub>DOC1</sub>  | • 6   | mV   |

| Discharge over current 2 protection voltage accuracy      | V <sub>DOC2A</sub> |                                               | -15 |                      | 15    | mV   |

| Discharge over current 2 protection voltage step          | V <sub>DOC2S</sub> |                                               |     | 2*V <sub>DOC1</sub>  |       | mV   |

| Discharge over current 2 protection delay time            | t <sub>DOC2</sub>  | 0.1µF capacitor on CDC pin with ±10% accuracy | 50  | 100                  | 150   | ms   |

| Discharge over current protection release voltage         | t <sub>DOCR</sub>  |                                               | 50  | 100                  | 150   | ms   |

| Short protection voltage                                  | V <sub>SC1</sub>   |                                               |     | 4* V <sub>DOC1</sub> |       | mV   |

| Short protection voltage accuracy                         | V <sub>SC1A</sub>  |                                               | -15 |                      | 15    | mV   |

| Short protection voltage step                             | V <sub>SC1S</sub>  |                                               |     | 4*V <sub>DOC1S</sub> |       | mV   |

| Short protection delay time                               | t <sub>SC</sub>    |                                               | 200 | 250                  | 300   | μs   |

| Discharge over current protection release delay time      | t <sub>SCR</sub>   |                                               | 50  | 100                  | 150   | ms   |

| Temperature Protection                                    |                    |                                               |     |                      |       |      |

| Charging high temperature protection threshold            | Тсот               |                                               | 46  | 50                   | 54    | °C   |

| Charging high temperature protection release threshold    | T <sub>COTR</sub>  |                                               | 41  | 45                   | 49    | °C   |

| Discharging high temperature protection threshold         | Трот               |                                               | 66  | 70                   | 74    | °C   |

| Discharging high temperature protection release threshold | T <sub>DOTR</sub>  |                                               | 51  | 55                   | 59    | °C   |

| Charging low temperature protection threshold             | Тсит               |                                               | -10 | -5                   | 0     | °C   |

| Charging low temperature protection release threshold     | T <sub>CUTR</sub>  |                                               | -5  | 0                    | 5     | °C   |

| Temperature protection delay time                         | t <sub>T</sub>     |                                               | 1.5 | 3                    | 5.5   | s    |

| Temperature protection release delay time                 | t <sub>TR</sub>    |                                               | 1.5 | 3                    | 5.5   | s    |

| Discharge status detection voltage                        | V <sub>DCH</sub>   |                                               | 2.5 | 5                    | 7.5   | mV   |

| Battery Cell Balance                                      |                    |                                               |     |                      |       | Т    |

| Balance operation voltage threshold                       | V <sub>OB</sub>    |                                               | 3.2 |                      | 4.375 | V    |

| Balance operation voltage accuracy                        | V <sub>OBA</sub>   |                                               | -25 |                      | 25    | mV   |

| Balance operation delay time                              | t <sub>BL</sub>    |                                               |     | 250                  |       | ms   |

| Balance impedance 1                                       | RBL1               | V <sub>CN</sub> =4.2V(N=1)                    |     | 1                    | 1.4   | kΩ   |

| Balance impedance 2                                       | RBL2               | V <sub>CN</sub> =4.2V(N=2,3,4,5)              | 75  | 100                  | 140   | Ω    |

# 9. Electrical CharacteriSITcs

$(T_A = 25^{\circ}C, unless otherwise noted.)$

| Parameters                           | Symbol             | Condition                             | Min                | Тур                  | Max  | Unit |

|--------------------------------------|--------------------|---------------------------------------|--------------------|----------------------|------|------|

| Others                               |                    |                                       |                    | ·                    |      |      |

| Operation voltage                    | $V_{DD}$           | CHG and DSG has correct output status | 3                  |                      | 40   | V    |

| Operation current (normal mode)      | I <sub>DD</sub>    |                                       |                    |                      | 20   | μΑ   |

| Operation current (sleep mode)       | I <sub>IDLE</sub>  |                                       |                    |                      | 5    | μA   |

| Sleep delay time                     | t <sub>UVP</sub>   |                                       | 20                 | 30                   | 40   | S    |

| Lowest adapter voltage               | V <sub>OCHA</sub>  |                                       |                    | 1                    | 1.5  | V    |

| Pull up resistor on CHSE             | R <sub>CHSE</sub>  |                                       | 800                | 1300                 | 1800 | kΩ   |

| Pull down resistor on VM             | R∨M                |                                       | 250                | 500                  | 700  | kΩ   |

| Logic high voltage of test pin       | V <sub>TESTH</sub> |                                       | 3.5                | 4                    | 4.5  | V    |

| Logic low voltage of test pin        | V <sub>TESTL</sub> |                                       | 0                  |                      | 0.3  | V    |

| Logic high voltage of SEL            | V <sub>SELH</sub>  |                                       | $V_{DD}$ -0.6      | V <sub>DD</sub> -0.1 |      | V    |

| Logic low voltage of SEL             | V <sub>SELL</sub>  |                                       |                    |                      | 0.6  | V    |

| Output current on CHG pin            | I <sub>CHG</sub>   |                                       | 4                  | 5                    | 6    | μA   |

| High voltage 1 output on DSG pin     | $V_{\text{DSG-1}}$ | V <sub>DD</sub> >13V                  | 11.5               | 12.5                 | 13.5 | V    |

| High voltage 2 output on DSG pin     | V <sub>DSG-2</sub> | V <sub>DD</sub> <13V                  | V <sub>DD</sub> -1 | V <sub>DD</sub> -0.7 |      | V    |

| Low voltage output on DSG pin        | V <sub>DSG-L</sub> |                                       |                    |                      | 0.2  | V    |

| Detect voltage threshold on CHSE pin | V <sub>CHSE</sub>  | Charge adapter detection              | 0.6                | 1                    | 1.5  | V    |

| Detect voltage threshold on VM pin   | V <sub>VM</sub>    | Load detection                        | 1.05               | 1.20                 | 1.35 | V    |

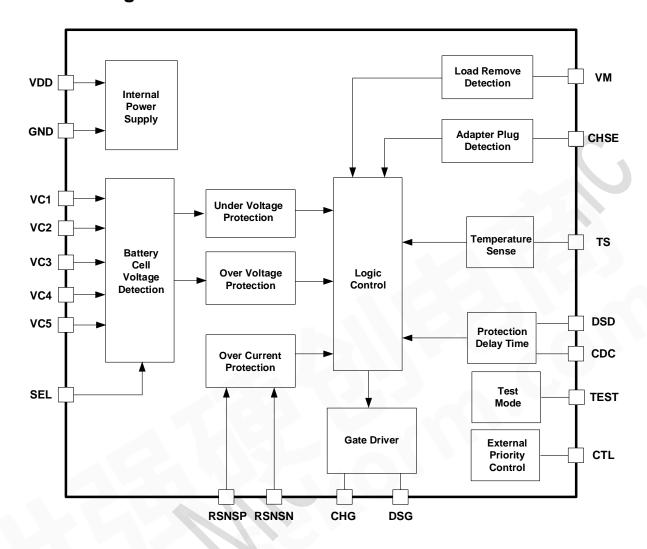

# 10. Block Diagram

Figure 4. SIT8995 block diagram

## 11. Function Description

#### 1. Normal Mode

SIT8995 enters normal mode if the following conditions are met:

- (1) All battery cell voltage is within over charge protection (V<sub>OV</sub>) and over discharge protection (V<sub>UV</sub>);

- (2) Differential voltage on RSNSP and RSNSN pins is smaller than over discharge current 1 protection voltage  $V_{DOC1}$ ;

- (3) Temperature detected from TS pin within charging high temperature protection  $T_{COT}$  and charging low temperature protection  $T_{CUT}$ ;

- (4) No any safety protection issue is noted.

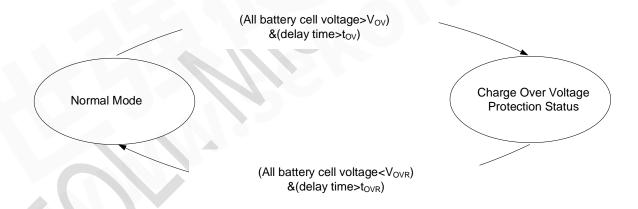

### 2. Charge Over Voltage Protection Status

SIT8995 enters into Charge Over Voltage Protection Status if the following conditions are met:

- (1) Any battery cell voltage is higher than charge over voltage protection V<sub>OV</sub>;

- (2) Duration time of condition (1) is longer than charge over voltage protection delay time  $t_{\text{OV}}$ . In charge over voltage protection status, CHG pin of SIT8995 is high impedance status.

Charge over voltage protection status is released if the following conditions are met:

- (1) All battery cell voltage is lower than  $V_{OV}$  when adapter is removed or all battery cell voltage is lower than charge over voltage protection release voltage  $V_{OVR}$  when adapter is plugged in.

- (2) Duration time of condition (1) is longer than charge over voltage protection release delay time  $t_{\text{OVR}}$ .

Figure 5. Charge over voltage protection status state transition diagram

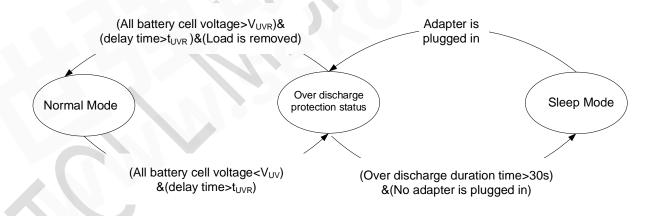

#### 3. Discharge Under Voltage Protection Status

SIT8995 enters into Discharge Under Voltage Protection Status if the following conditions are met:

- (1) Any battery cell voltage is lower than over discharge protection V<sub>UV</sub>;

- (2) Duration time of condition (1) is longer than over discharge under voltage protection release delay time  $t_{UV}$ , CHG pin of SIT8995 is high impedance status and DSG pin output is low.

After load lock is released, the discharge under voltage protection status is released if the following conditions are met:

www.toll-semi.com TMI and SUNTO are the brands of TOLL microelectronic

SIT8995 V1.2 – 2021.03

- (1) Adapter plugged in is detected and all battery cells voltage is higher than  $V_{UV}$ , or the load is removed and all battery cells voltage is higher than discharge under voltage protection release voltage  $V_{UVR}$ ;

- (2) Duration time of condition (1) is longer than over discharge protection release delay time t<sub>UVR</sub>.

**Note 3:** Load lock status is released and 64ms duration time after Load lock status is released if the following conditions are met:

- (1) Load is removed;

- (2) Adapter is plugged in.

#### 4. Sleep Mode

SIT8995 enters into Sleep Mode if the following conditions are met:

- (1) Duration time of discharge under voltage protection status is longer than sleep delay time t<sub>UVP</sub> (32s Typ.);

- (2) No adapter is plugged in (condition of no adapter is plugged in: CHSE Voltage > V<sub>CHSEH</sub>).

**Note 4**: If duration time of over discharge under voltage protection status is longer than 30s after discharge status, <u>SIT8995</u> pulls internal resistor up to VDD on CHSE pin to detect adapter is plugged in or not.

In sleep mode, <u>SIT8995</u> shuts down almost system block. Voltage, current and temperature detection ceases. CHG pin of SIT8995 is high impedance status and DSG pin output is low.

SIT8995 exits sleep mode if the following conditions are met:

Adapter is plugged in (Condition of adapter is plugged in: CHSE voltage≤ V<sub>CHSE</sub>).

Figure 6. Discharge under voltage protection status state transition diagram

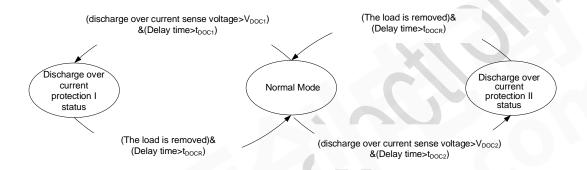

#### 5. Discharge Over Current Protection Status

<u>SIT8995</u> has two stage discharge over current protection. Over current 1 protection voltage  $V_{DOC1}$  is smaller than over current 1 protection voltage  $V_{DOC2}$ , and delay time of over current 1 protection  $t_{DOC1}$  is longer than delay time of over current 1 protection  $t_{DOC2}$ .

SIT8995 enters int discharge over current protection status if the following conditions are met:

(1) Differential voltage on RSNSP and RSNSN pin is higher than discharge over current 1 protection

TMÍ SUNTO

www.toll-semi.com

voltage V<sub>DOC1</sub> ( or discharge over current 2 protection voltage V<sub>DOC2</sub>);

(2) Duration time of condition (1) is longer than delay time of over current 1 protection  $t_{DOC1}$  (or delay time of over current 2 protection  $t_{DOC2}$ ).

CHG pin of SIT8995 is high impedance status and DSG pin output is low.

Discharge over current protection status is released if the following conditions are met:

- (1) The load is removed (Condition of load is removed: voltage on VM is lower than V<sub>VM</sub>);

- (2) Duration time of condition (1) is longer than discharge over current protection released delay time  $t_{DOCR}$ .

**Note 5:** After discharge over current protection happens, VM pin of <u>SIT8995</u> is pulled down to GND by internal resistor to detect that the load is removed or not.

Figure 7. Discharge over current protection status state transition diagram

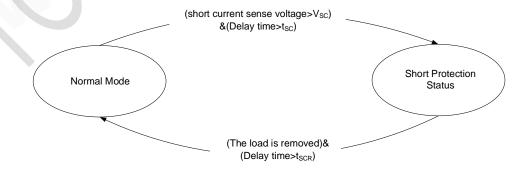

#### 6. Short Protection Status

SIT8995 enters int short protection status if the following conditions are met:

- (1) Differential voltage on RSNSP and RSNSN pin is higher than short protection voltage V<sub>SC</sub>;

- (2) Duration time of condition (1) is longer than short protection delay time t<sub>SC</sub>.

Short protection status is released if the following conditions are met:

- (1) The load is removed (Condition of load is removed: voltage on VM is lower than V<sub>VM</sub>);

- (2) Duration time of condition (1) is longer than discharge over current protection released delay time  $t_{SCR}$ .

**Note 6:** After short protection happens, VM pin of <u>SIT8995</u> is pulled down to GND by internal resistor to detect that the load is removed or not.

Figure 8. Short protection status state transition diagram

www.toll-semi.com TMI sunto TMI and SUNTO are the brands of TOLL microelectronic

#### 7. Charge Over Current Protection

SIT8995 enters charge over current protection status if the following conditions are met::

- (1) Differential voltage on RSNSP and RSNSN pin is higher than charge over current protection voltage V<sub>COC</sub>;

- (2) Duration time of condition (1) is longer than charge over current protection delay time  $t_{\text{COC}}$ . In charge over current protection status. CHG pin of <u>SIT8995</u> is high impedance status.

Charge over current protection status is released if the following conditions are met:

- (1) Charger adapter is plugged out;

- (2) Delay time is longer than charge over current protection release delay time t<sub>COCR</sub>.

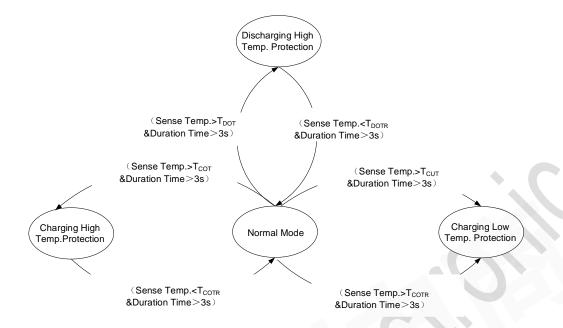

#### 8. Temperature Protection

When NTC resistor (103AT ( $\beta$  = 3435) is recommended) is used, <u>SIT8995</u> temperature protection is active. It includes charging high temperature protection, charging low temperature protection and discharging high temperature protection. The temperature protection function is described as below:

### 8.1 Charging High Temperature Protection Status

SIT8995 enters charging high temperature protection status if the following conditions are met:

- (1) Sense temperature is higher than charging high temperature protection threshold T<sub>COT</sub>;

- (2) the duration time is longer than 3s.

CHG pin of SIT8995 is high impedance status in charging condition.

Charging high temperature protection status is released if the following conditions are met:

- (1) Sense temperature is lower than charging high temperature protection release threshold T<sub>COTR</sub>.

- (2) The duration time is longer than 3s.

#### 8.2 Charging Low Temperature Protection Status

SIT8995 enters charging low temperature protection status if the following conditions are met:

- (1) Sense temperature is lower than charging low temperature protection threshold T<sub>CUT</sub>;

- (2) The duration time is longer than 3s.

CHG pin of SIT8995 is high impedance status in charging condition.

Charging low temperature protection status is released if the following conditions are met:

- (1) Sense temperature is lower than charging high temperature protection release threshold T<sub>CUTR</sub>;

- (2) The duration time is longer than 3s.

#### 8.3 Discharging High Temperature Protection Status

SIT8995 enters charging high temperature protection status if the following conditions are met:

- (1) Sense temperature is higher than charging high temperature protection threshold T<sub>DOT</sub>;

- (2) The duration time is longer than 3s.

CHG pin of SIT8995 is high impedance status and DSG output is low in discharging condition.

Discharging high temperature protection status is released if the following conditions are met:

- (1) Sense temperature is lower than charging high temperature protection release threshold T<sub>DOTR</sub>;

- (2) The duration time is longer than 3s.

www.toll-semi.com

Figure 9. Temperature Protection Status State transition diagram

NTC thermal resistor 103AT ( $\beta$  = 3435) is recommended in <u>SIT8995</u> application. The below table shows NTC resistance vs. Temperature.:

| Temperature (°C) | 103AT Resistance(kΩ) | Resistance Tolerance (kΩ) |

|------------------|----------------------|---------------------------|

| -20              | 67.77                | 72.72-63.20               |

| -15              | 53.41                | 57.11-49.98               |

| -10              | 42.47                | 45.27 - 39.86             |

| -5               | 33.90                | 36.02 - 31.92             |

| 0                | 27.28                | 28.90 - 25.76             |

| 5                | 22.05                | 23.29 - 20.88             |

| 25               | 10                   | 9.700 - 10.30             |

| 45               | 4.911                | 5.094 - 4.735             |

| 47               | 4.554                | 4.691 - 4.417             |

| 50               | 4.16                 | 4.306 - 4.018             |

| 55               | 3.536                | 3.654 - 3.421             |

| 60               | 3.02                 | 3.115 - 2.927             |

| 65               | 2.588                | 2.665 - 2.513             |

| 70               | 2.288                | 2.291 - 2.167             |

Table 1. 103AT ( $\beta$  = 3435) resistance vs temperature

#### 9. Battery Cell Voltage Balance

In <u>SIT8995</u> application, when any battery cell voltage is higher than balance operation voltage threshold  $V_{OB}$  and duration time is longer than balance active delay time  $T_{BL}$ , the internal balance circuits in <u>SIT8995</u> is active to balance charging current of battery cell. The function calls battery cell voltage balance. <u>SIT8995</u> adapts parity balance method. The adjacent battery cell balance is not occurring at the same time. Balance cycle is 250ms.

www.toll-semi.com TMI and SUNTO are the brands of TOLL microelectronic

SIT8995 V1.2 – 2021.03

The system exits battery balance condition if the following conditions are met:

- (1) Battery cell voltage is lower than V<sub>OB</sub>;

- (2) Temperature protection, discharge protection or charge protection events occurrence.

#### 10. Charge and Discharge Status Detection

Charge and discharge status are determined by RSNSP pin voltage. If the voltage on RSNSP pin is higher than discharge status detection voltage  $V_{DCH}$ , <u>SIT8995</u> is in discharging status. <u>SIT8995</u> system is in charge status except discharge status.

#### 11. 0V Charge Function

Battery pack voltage cannot be smaller than 1.5V, when adapter voltage is larger than  $V_{\text{OCHA}}$ . SIT8995 enable charging from adapter to battery pack. Requirement to lowest voltage of adapter depends on turn on threshold voltage of charge MOSFET used in application

Downloaded From Oneyac.com

15

# 12. Function Configuration

### 1. SEL Pin Configuration

SEL pin of SIT8995 selects 4 cells or 5 cells application. Please follows the below table:

| SEL | Function           |

|-----|--------------------|

| GND | 5 cells protection |

| VDD | 4 cells protection |

### 2. CTL Pin Configuration

CTL pin selects output status of CHG and DSG pin, and it has higher priority than internal protection circuits.

| CTL | DSG    | CHG    |

|-----|--------|--------|

| VDD | GND    | Hi-Z   |

| GND | Normal | Normal |

### 3. Delay Time Setting

In <u>SIT8995</u> application, partly protection delay time and protection release delay time can be set by external capacitor. The delay time can refer the below table:

| Item                                                  | Symbol            | Related Setup                                  | Delay time                                                          |

|-------------------------------------------------------|-------------------|------------------------------------------------|---------------------------------------------------------------------|

| Charge over voltage protection delay time             | t <sub>OV</sub>   | Internal fixed                                 | 1s                                                                  |

| Charge over voltage protection release delay time     | t <sub>OVR</sub>  | Internal fixed                                 | 160ms                                                               |

| Charge over current protection delay time             | tcoc              | Internal fixed                                 | 1s                                                                  |

| Charge over current protection release delay time     | tcocr             | Internal fixed                                 | 100ms                                                               |

| Discharge under voltage protection delay time         | tuv               | External capacitor C <sub>DSD</sub> on DSD pin | 1s ×C <sub>DSD</sub> /0.1µF                                         |

| Discharge under voltage protection release delay time | tuvr              | External capacitor C <sub>DSD</sub> on DSD pin | 100ms × C <sub>DSD</sub> /0.1μF                                     |

| Discharge over current 1 protection delay time        | t <sub>DOC1</sub> | External capacitor C <sub>CDC</sub> on CDC pin | 1s × C <sub>CDC</sub> /0.1μF                                        |

| Discharge over current 2 protection delay time        | t <sub>DOC2</sub> | External capacitor C <sub>CDC</sub> on CDC pin | 0.1s × C <sub>CDC</sub> /0.1μF 或<br>0.35s × C <sub>CDC</sub> /0.1μF |

| Discharge over current protection release delay time  | t <sub>DOCR</sub> | External capacitor Ccbc on CDC pin             | 0.1s×C <sub>CDC</sub> /0.1μF                                        |

| Short protection delay time                           | t <sub>SC</sub>   | Internal fixed                                 | 250µs                                                               |

| Short protection release delay time                   | t <sub>SCR</sub>  | External capacitor CcDc on CDC pin             | 1s×Cccc/0.1μF 或<br>0.1s×Cccc/0.1μF                                  |

| Temperature protection delay time                     | t⊤                | Internal fixed                                 | 3s                                                                  |

| Temperature protection release delay time             | t <sub>TR</sub>   | Internal fixed                                 | 3s                                                                  |

| Sleep mode delay time                                 | $t_{\sf UVP}$     | Internal fixed                                 | 32s                                                                 |

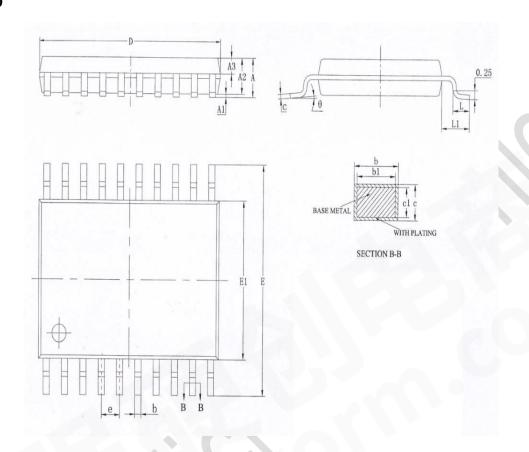

# 13. Package Information

## TSSOP20

Unit: mm

| Symbol [ | Dimen | Dimensions In Millimeters |      |        | Dimensions In Millimeters |      |      |  |

|----------|-------|---------------------------|------|--------|---------------------------|------|------|--|

| Symbol   | Min   | Nom                       | Max  | Symbol | Min                       | Nom  | Max  |  |

| Α        | -     | -                         | 1.20 | D      | 6.40                      | 6.50 | 6.60 |  |

| A1       | 0.05  | -                         | 0.15 | E1     | 4.30                      | 4.40 | 4.50 |  |

| A2       | 0.80  | 1.00                      | 1.05 | Е      | 6.20                      | 6.40 | 6.60 |  |

| A3       | 0.39  | 0.44                      | 0.49 | е      | 0.65BSC                   |      |      |  |

| b        | 0.2   | -                         | 0.30 | L      | 0.45                      | 0.60 | 0.75 |  |

| b1       | 0.19  | 0.22                      | 0.25 | L1     | 1.00REF                   |      |      |  |

| С        | 0.13  | -                         | 0.19 | θ      | 0                         | -    | 8°   |  |

| c1       | 0.12  | 0.13                      | 0.14 |        |                           |      |      |  |

# **Important Notification**

This document only provides product information. Xi'an TOLL Microelectronic Inc. (TMI) reserves the right to make corrections, modifications, enhancements, improvements, and other changes to its products and to discontinue any product without notice at any time.

Xi'an TOLL Microelectronic Inc. (TMI) cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a TMI product. No circuit patent licenses are implied.

All rights are reserved by Xi'an TOLL Microelectronic Inc. http:// www.toll-semi.com

# 单击下面可查看定价,库存,交付和生命周期等信息