# 8k, 16k bit EEPROMs for direct connection to serial ports

# BR9080AF-W / BR9080ARFV-W / BR9080ARFVM-W / BR9016AF-W / BR9016ARFV-W / BR9016ARFVM-W

The BR9080A and BR9016A series are serial EEPROMs that can be connected directly to a serial port and can be erased and written electrically. Writing and reading is performed in word units, using four types of operation commands. Communication occurs though  $\overline{CS}$ ,  $\overline{SK}$ , DI, and DO pins,  $\overline{WC}$  pin control is used to initiate a write disabled state, enabling these EEPROMs to be used as one-time ROMs. During writing, operation is checked via the internal status check.

#### Applications

Movie, camera, cordless telephones, car stereos, VCRs, TVs, DIP switches, and other battery-powered equipment requiring low voltage and low current

#### Features

- 1) BR9080AF-W / ARFV-W / ARFVM-W (8k bit) : 512 words  $\times$ 16 bits BR9016AF-W / ARFV-W / ARFVM-W (16k bit) : 1024 words  $\times$  16bits

- 2) Single power supply operation

- 3) Serial data input and output

- 4) Automatic erase-before-write

- 5) Low current consumption Active (5V): 5mA (max.)

- Standby (5V): 3µA (max.)

- 6) Noise filter built into SK pin

- Write protection when Vcc is low Inhibition on inadvertant write with the WC pin.

- 8) SOP8 / SSOP-B8 / MSOP8

- 9) High reliability CMOS process

- 10) 100,000 ERASE / WRITE cycles

- 11) 10 years Data Retention

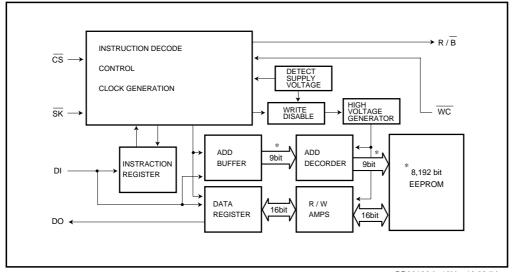

#### Block diagram

\* BR9016A is 10bit, 16,384bit BR9080A is 9bit, 8,192bit

#### Pin descriptions

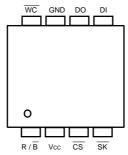

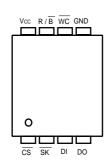

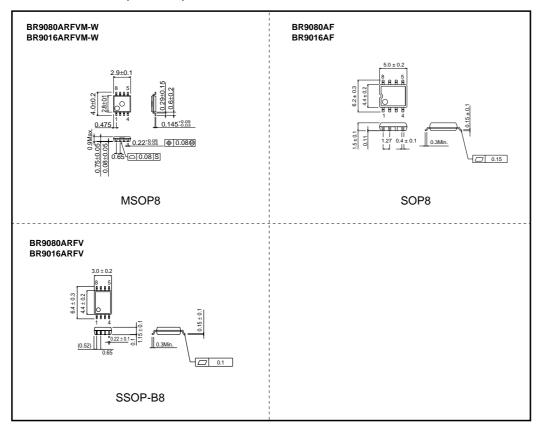

BR9080ARFVM : MSOP8

BR9080AF BR9016AF: SOP8

BR9080ARFV BR9016ARFV: SSOP-B8

Fig.1

| Pin No.     |     | Pin name | Function                            |  |  |  |

|-------------|-----|----------|-------------------------------------|--|--|--|

| MSOP / SSOP | SOP | Pinname  | Function                            |  |  |  |

| 1           | 3   | CS       | Chip Select Control                 |  |  |  |

| 2           | 4   | SK       | Serial Data Clock Input             |  |  |  |

| 3           | 5   | DI       | Op code, address, Serial Data Input |  |  |  |

| 4           | 6   | DO       | Serial Data Output                  |  |  |  |

| 5           | 7   | GND      | Ground 0V                           |  |  |  |

| 6           | 8   | WC       | Write Control Input                 |  |  |  |

| 7           | 1   | R/B      | READY / BUSY Output                 |  |  |  |

| 8           | 2   | Vcc      | Power supply                        |  |  |  |

### BR9080AF-W / BR9080ARFV-W / BR9080ARFVM-W / BR9016AF-W / BR9016ARFV-W / BR9016ARFVM-W

#### ●Absolute maximum ratings (Ta=25°C)

| Parameter             | Symbol | Lin            | Unit  |    |  |

|-----------------------|--------|----------------|-------|----|--|

| Supply voltage        | Vcc    | -0.3~+7.0      |       | V  |  |

|                       |        | SOP8           | 450*1 |    |  |

| Power dissipation     | Pd     | SSOP-B8        | 300*2 | mW |  |

|                       |        | MSOP8          | 310*3 |    |  |

| Storage temperature   | Tstg   | -65~           | +125  | °C |  |

| Operation temperature | Topr   | <b>−40~+85</b> |       | °C |  |

| Input voltage         | _      | -0.3~V         | V     |    |  |

<sup>\*1</sup> Reduced by 4.5mW for each increase in Ta of 1°C over 25°C.

\*2 Reduced by 3.0mW for each increase in Ta of 1°C over 25°C.

\*3 Reduced by 3.1mW for each increase in Ta of 1°C over 25°C.

#### ●Recommended operating conditions (Ta=25°C)

| Parameter            | Symbol | Min. | Тур. | Max. | Unit |   |

|----------------------|--------|------|------|------|------|---|

| Power supply voltage | WRITE  | Vac  | 2.7  | -    | 5.5  | V |

|                      | READ   | Vcc  | 2.7  | _    | 5.5  | V |

| Input voltage        | Vin    | 0    | _    | Vcc  | V    |   |

# BR9080AF-W / BR9080ARFV-W / BR9080ARFVM-W / BR9016AF-W / BR9016ARFV-W / BR9016ARFVM-W

#### •Electrical characteristics

BR9080AF-W / ARFV-W / ARFVM-W, BR9016AF-W / ARFV-W / ARFVM-W : 5V (Unless otherwise noted, Ta=–40~85°C, Vcc=2.7V~5.5V)

| Parameter                  | Symbol           | Min.    | Тур. | Max.    | Unit | Conditions                           |

|----------------------------|------------------|---------|------|---------|------|--------------------------------------|

| Input low level voltage 1  | VIL1             | _       | -    | 0.3×Vcc | V    | DI pin                               |

| Input high level voltage 1 | V <sub>IH1</sub> | 0.7×Vcc | -    | _       | V    | DI pin                               |

| Input low level voltage 2  | VIL2             | _       | -    | 0.2×Vcc | V    | CS, SK, WC pin                       |

| Input high level voltage 2 | V <sub>IH2</sub> | 0.8×Vcc | _    | -       | V    | CS, SK, WC pin                       |

| Output low level voltage   | Vol              | 0       | -    | 0.4     | V    | IoL=2.1mA                            |

| Output high level voltage  | Vон              | Vcc-0.4 | 1    | Vcc     | V    | Ioн=-0.4mA                           |

| Input leak current         | lu               | -1      | ı    | 1       | μΑ   | Vin=0V~Vcc                           |

| Output leak current        | ILO              | -1      | 1    | 1       | μΑ   | Vout=0V~Vcc, CS=Vcc                  |

| Operating current          | Icc1             | _       | ı    | 5       | mA   | fsκ=2MHz tE / W=10ms (WRITE)         |

| Operating current          | Icc2             | _       | _    | 3       | mA   | fsκ=2MHz (READ)                      |

| Standby current            | IsB              | _       | -    | 3       | μΑ   | CS / SK / DI / WC=Vcc DO, R / B=OPEN |

| SK frequency               | fsк              | _       | -    | 2       | MHz  | -                                    |

### BR9080AF-W / ARFV-W / ARFVM-W, BR9016AF-W / ARFV-W / ARFVM-W : 3V (Unless otherwise noted, Ta= $-40-85^{\circ}$ C, Vcc=2.7V-3.3V)

| Parameter                  | Symbol           | Min.    | Тур. | Max.    | Unit | Conditions                           |

|----------------------------|------------------|---------|------|---------|------|--------------------------------------|

| Input low level voltage 1  | VIL1             | _       | -    | 0.3×Vcc | V    | DI pin                               |

| Input high level voltage 1 | V <sub>IH1</sub> | 0.7×Vcc | -    | -       | V    | DI pin                               |

| Input low level voltage 2  | V <sub>IL2</sub> | _       | _    | 0.2×Vcc | V    | CS, SK, WC pin                       |

| Input high level voltage 2 | V <sub>IH2</sub> | 0.8×Vcc | _    | -       | V    | CS, SK, WC pin                       |

| Output low level voltage   | Vol              | 0       | -    | 0.4     | V    | IoL=100μA                            |

| Output high level voltage  | Vон              | Vcc-0.4 | -    | Vcc     | V    | Ioн=-100μA                           |

| Input leak current         | lu               | -1      | -    | 1       | μΑ   | Vin=0V~Vcc                           |

| Output leak current        | ILO              | -1      | _    | 1       | μΑ   | Vout=0V~Vcc, CS=Vcc                  |

| Operating current          | Icc1             | _       | _    | 3       | mA   | fsκ=2MHz tE / W=10ms (WRITE)         |

| Operating current          | Icc2             | _       | -    | 0.75    | mA   | fsk=2MHz (READ)                      |

| Standby current            | IsB              | _       | -    | 2       | μΑ   | CS / SK / DI / WC=Vcc DO, R / B=OPEN |

| SK frequency               | fsк              | _       | _    | 2       | MHz  | -                                    |

Not designed for radiation resistance

#### Operating timing characteristics

BR9080AF-W / ARFV-W / ARFVM-W, BR9016AF-W / ARFV-W / ARFVM-W (Unless otherwise noted, Ta=-40~85°C, Vcc=2.7V~5.5V)

| Parameter                                              | Symbol           | Min. | Тур. | Max. | Unit |

|--------------------------------------------------------|------------------|------|------|------|------|

| CS setup time                                          | fcss             | 100  | -    | -    | ns   |

| CS hold time                                           | tсsн             | 100  | _    | -    | ns   |

| Data setup time                                        | tois             | 100  | -    | -    | ns   |

| Data hold time                                         | tын              | 100  | _    | -    | ns   |

| DO rise delay time                                     | <b>t</b> PD1     | -    | _    | 150  | ns   |

| DO fall delay time                                     | t <sub>PD0</sub> | -    | _    | 150  | ns   |

| Self-timing programming cycle                          | <b>t</b> E/W     | -    | -    | 10   | ms   |

| CS minimum high level time                             | tcs              | 250  | _    | _    | ns   |

| READY / BUSY display valid time                        | tsv              | -    | _    | 150  | ns   |

| Time when DO goes HIGH-Z (via $\overline{\text{CS}}$ ) | tон              | 0    | _    | 150  | ns   |

| Data clock high level time                             | twн              | 230  | -    | -    | ns   |

| Data clock low level time                              | twL              | 230  | _    | -    | ns   |

| Write control setup time                               | twcs             | 0    | _    | -    | ns   |

| Write control hold time                                | twcн             | 0    | -    | -    | ns   |

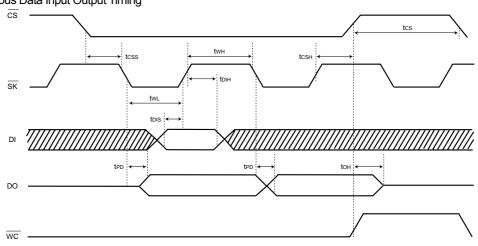

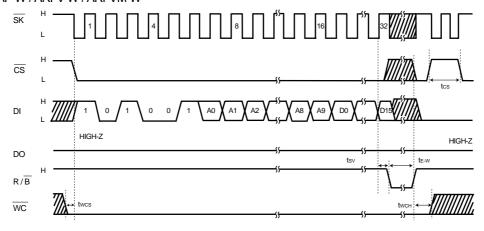

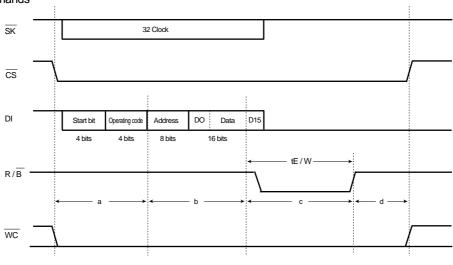

#### Timing chart

Synchronous Data Input Output Timing

Fig.2

- Input data are clocked in to DI at the rising edge of the clock  $(\overline{SK})\!.$

- Output data will toggle on the falling edge of the  $\overline{SK}$  clock.

- $\cdot$  The  $\overline{\text{WC}}$  pin does not have any effect on the READ, EWEN and EWDS operations.

#### Circuit operation

(1) Command mode BR9080A

| Instruction         | Start Bit | Op Code | Address                 | Data            |

|---------------------|-----------|---------|-------------------------|-----------------|

| Read (READ)         | 1010      | 100 A0  | A1 A2 A3 A4 A5 A6 A7 A8 |                 |

| Write (WRITE)       | 1010      | 010 A0  | A1 A2 A3 A4 A5 A6 A7 A8 | D0 D1 – D14 D15 |

| Write enable (WEN)  | 1010      | 0011    | * * * * * * * *         |                 |

| Write disable (WDS) | 1010      | 0000    | * * * * * * * *         |                 |

\* : Means either VIH or VIL Address and data are transferred from LSB.

#### BR9016A

| Instruction         | Start Bit | Op Code  | Address                 | Data            |

|---------------------|-----------|----------|-------------------------|-----------------|

| Read (READ)         | 1010      | 10 A0 A1 | A2 A3 A4 A5 A6 A7 A8 A9 |                 |

| Write (WRITE)       | 1010      | 01 A0 A1 | A2 A3 A4 A5 A6 A7 A8 A9 | D0 D1 – D14 D15 |

| Write enable (WEN)  | 1010      | 0011     | * * * * * * * *         |                 |

| Write disable (WDS) | 1010      | 0000     | * * * * * * * *         |                 |

\*: Means either VIH or VIL Address and data are transferred from LSB.

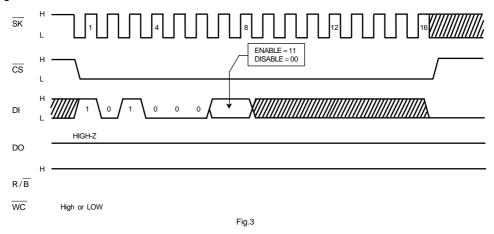

#### (2) Writing enabled / disabled

1) When  $\overline{\text{CS}}$  is "HIGH" during power up, BR9080AF-W / ARFV-W / ARFVM-W, BR9016AF-W / ARFV-W / ARF comes up in the write disabled (WDS) state. In order to be programmable, it must receive a write enable (WEN) instruction.

The device remains programmable until a disable (WDS) instruction is entered, or until it is powered down.

2) It is unnecessary to add the clock after 16th clock.

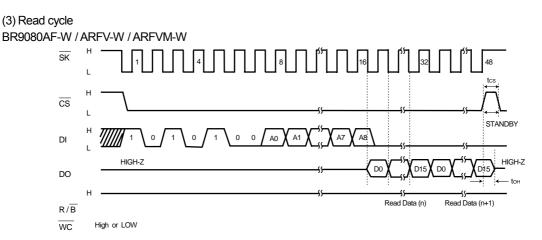

Fig.4 BR9080AF-W / ARFV-W / ARFVM-W

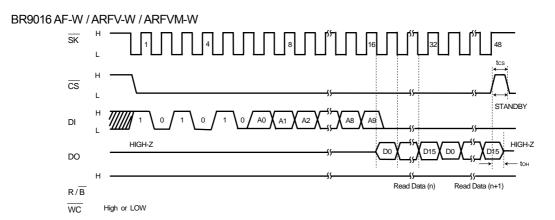

Fig.5 BR9016AF-W / ARFV-W / ARFVM-W

- 1) After the fall of the 16th clock pulse, 16-bit data is output from the DO pin in synchronization with the falling edge of the  $\overline{SK}$  signal.

- (DO output changes at a time lag of tpd, tpd because of internal circuit delay following the falling edge of the  $\overline{SK}$  signal. During the tpd and tpd timing, the tpd time should be assured before data is read, to avoid the previous data being lost. See the synchronized data input / output timing chart in Fig.2.)

- 2) The data stored in the next address is clocked out of the device on the falling edge of 32nd clock. The data stored in the upper address every 16 clocks is output sequentially by the continual  $\overline{SK}$  input. Also the read operation is reset by  $\overline{CS}$  High.

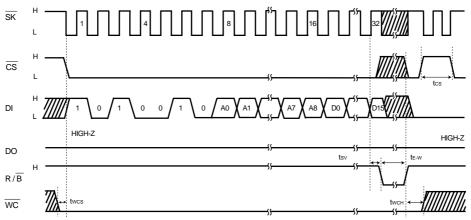

#### (4) Write cycle BR9080AF-W / ARFV-W / ARFVM-W

Fig.6 BR9080AF-W / ARFV-W / ARFVM-W

#### BR9016 AF-W / ARFV-W / ARFVM-W

Fig.7 BR9016AF-W / ARFV-W / ARFVM-W

- 1) At the rising edge of 32nd clock,  $R/\overline{B}$  pin will be come out "LOW" after the specified time delay (tSV).

- 2) From above edge R /  $\overline{B}$  will indicate the ready / busy status of the chip: "LOW" indicated programming is all in progress: "HIGH" indicates the write cycle is complete and this part is ready for another instruction.

- 3) During the input of Write command,  $\overline{CS}$  must be "LOW". However, once the write operation started,  $\overline{CS}$  could be either "HIGH" or "LOW".

- 4) If  $\overline{\text{WC}}$  becomes "HIGH" during Write Cycle, the write operation is halted. In this case, the address data in writing is no guaranteed. It is necessary to rewrite it.

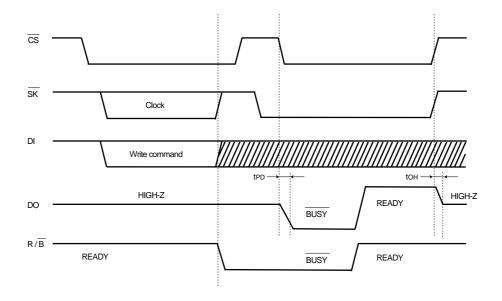

#### (5) READY / BUSY display

(R /  $\overline{\rm B}$  pin and DO pin: BR9080AF-W / ARFV-W / ARFVM-W, BR9016AF-W / ARFV-W / ARFVM-W)

- 1) This display outputs the internal status signal; the R /  $\overline{B}$  pin outputs the HIGH or LOW status at all times. The display can also be output from the DO pin. Following completion of the writing command, if  $\overline{CS}$  falls while  $\overline{SK}$  is LOW, either HIGH or LOW is output. (The display can also be output without using the R /  $\overline{B}$  pin, leaving it open.)

- 2) When writing data to a memory cell, the READY /  $\overline{BUSY}$  display is output from the rise of the 32nd clock pulse of the  $\overline{SK}$  signal after tSV, from the R /  $\overline{B}$  pin.

$R/\overline{B}$  display = LOW: writing in progress

(The internal timer circuit is activated, and after the tE / W timing has been created, the timer circuit stops automatically. Writing of data to the memory cell is done during the tE / W timing, during which time other commands cannot be received.)

$R/\overline{B}$  display = HIGH: command standby state

(Writing of data to the memory cell has been completed and the next command can be received.)

Fig.8 R/B Status Output timing chart

1) DO will output R /  $\overline{B}$  status after  $\overline{CS}$  is held low during  $\overline{SK}$ =L, until  $\overline{CS}$  is held high.

Note: The document may be strategic technical data subject to COCOM regulations.

## BR9080AF-W / BR9080ARFV-W / BR9080ARFVM-W / BR9016AF-W / BR9016ARFVM-W

#### Operation notes

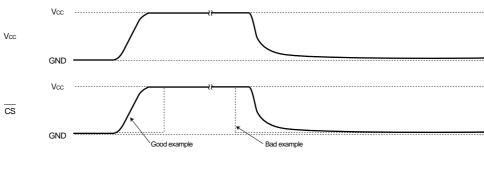

- (1) Turning the power supply on and off

- 1) When the power supply is turned on and off,  $\overline{\text{CS}}$  should be set to HIGH (=Vcc).

- 2) When  $\overline{\text{CS}}$  is LOW, the command input reception state (active) is entered. If the power supply is turned on in this state, erroneous operations and erroneous writing can occur because of noise and other factors. To avoid this, make sure  $\overline{\text{CS}}$  is set to HIGH (=Vcc) before turning on the power supply.

(Good example) Here, the  $\overline{CS}$  pin is pulled up to Vcc.

When turning off the power supply, wait at least 10msec before turning it on again. Failing to observe this condition can result in the internal circuit failing to be reset when the power supply is turned on.

(Bad example)  $\overline{CS}$  is LOW when the power supply is turned on or off.

In this case, because  $\overline{\text{CS}}$  remains LOW, the EEPROM may perform erroneous operations or write erroneous data because of noise or other factors.

\* Please be aware that the case shown in this example can also occur if  $\overline{\text{CS}}$  input is HIGH-Z.

Fig.9

#### (2) Noise countermeasures

#### 1) SK noise

If noise occurs at the rise of the  $\overline{SK}$  clock input, the clock is assumed to be excessive, and this can cause malfunction because the bits are out of alignment.

#### 2) WC noise

During a writing operation, noise at the  $\overline{WC}$  pin can be erroneously judged to be data, and this can cause writing to be forcibly interrupted.

#### 3) Vcc noise

Noise and surges on the power supply line can cause malfunction. We recommend installing a bypass capacitor between the power supply and ground to eliminate this problem.

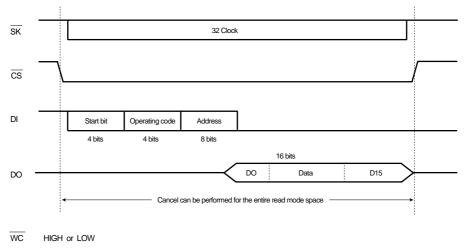

#### (3) Canceling modes

#### 1) Read commands

Fig.10

#### Cancellation method: CS HIGH

#### 2) Write commands

Fig.11

#### Canceling methods

- a : Canceled by setting CS HIGH. The WC pin is not involved.

- b: If the WC pin goes HIGH for even a second, writing is forcibly interrupted. Cancellation occurs even if the CS pin is HIGH. At this point, data has not been written to the memory, so the data in the designated address has not yet been changed.

- c: The operation is forcibly canceled by setting the WC pin to HIGH or turning off the power supply (although we do not recommend using this method). The data in the designated address is not guaranteed and should be written once again.

- d: If  $\overline{CS}$  is set to HIGH while the R /  $\overline{B}$  signal is HIGH (following the tE / W timing), the IC is reset internally, and waits for the next command to be input.

#### ●External dimension (Units : mm)

#### **Notes**

- No technical content pages of this document may be reproduced in any form or transmitted by any means without prior permission of ROHM CO.,LTD.

- The contents described herein are subject to change without notice. The specifications for the

product described in this document are for reference only. Upon actual use, therefore, please request

that specifications to be separately delivered.

- Application circuit diagrams and circuit constants contained herein are shown as examples of standard

use and operation. Please pay careful attention to the peripheral conditions when designing circuits

and deciding upon circuit constants in the set.

- Any data, including, but not limited to application circuit diagrams information, described herein are intended only as illustrations of such devices and not as the specifications for such devices. ROHM CO.,LTD. disclaims any warranty that any use of such devices shall be free from infringement of any third party's intellectual property rights or other proprietary rights, and further, assumes no liability of whatsoever nature in the event of any such infringement, or arising from or connected with or related to the use of such devices.

- Upon the sale of any such devices, other than for buyer's right to use such devices itself, resell or

otherwise dispose of the same, no express or implied right or license to practice or commercially

exploit any intellectual property rights or other proprietary rights owned or controlled by

- ROHM CO., LTD. is granted to any such buyer.

- Products listed in this document use silicon as a basic material.

Products listed in this document are no antiradiation design.

The products listed in this document are designed to be used with ordinary electronic equipment or devices (such as audio visual equipment, office-automation equipment, communications devices, electrical appliances and electronic toys).

Should you intend to use these products with equipment or devices which require an extremely high level of reliability and the malfunction of with would directly endanger human life (such as medical instruments, transportation equipment, aerospace machinery, nuclear-reactor controllers, fuel controllers and other safety devices), please be sure to consult with our sales representative in advance.

About Export Control Order in Japan

Products described herein are the objects of controlled goods in Annex 1 (Item 16) of Export Trade Control Order in Japan.

In case of export from Japan, please confirm if it applies to "objective" criteria or an "informed" (by MITI clause) on the basis of "catch all controls for Non-Proliferation of Weapons of Mass Destruction.

### 单击下面可查看定价,库存,交付和生命周期等信息

>>ROHM Semiconductor(罗姆)