### High Efficiency, 1A, 100V Input Synchronous Step Down Regulator

### **General Description**

The SQ27001 develops a high efficiency synchronous step-down DC/DC converter capable of delivering 1A current. The SQ27001 operates over a wide input voltage range from 7V to 100V and integrates main switch and synchronous switch with very low  $R_{\rm DS(ON)}$  to minimize the conduction loss. The SQ27001 always operates under Continuous Conduction Mode. The device adopts the instant PWM architecture to achieve fast transient responses for high step down applications.

### **Ordering Information**

| Ordering Number | Package type | Note |

|-----------------|--------------|------|

| SQ27001FCC      | SO8E         |      |

#### **Features**

- Low  $R_{DS(ON)}$  for Internal Switches (Top/Bottom):  $500m\Omega/240m\Omega$

- 7-100V Input Voltage Range

- 1A Output Current Capability

- Constant On-time Control

- Instant PWM Architecture to Achieve Fast Transient Responses

- Programmable Switching Frequency Range: 200kHz ~600kHz

- 2ms Internal Soft-start Limits the Inrush Current

- Precise ±2% 1.225V Reference over -40°C to +125°C Temperature Range

- Cycle-by-cycle Peak Current Limit

- Over Temperature Protection with Auto Recovery

- RoHS Compliant and Halogen Free

- Compact Package SO8E

### **Applications**

- Isolated Telecom Bias Supply

- Secondary High Voltage Post Regulator

- Automotive Systems

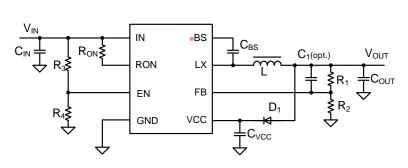

### **Typical Applications**

Figure 1. Schematic Diagram

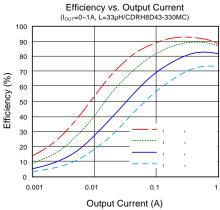

Figure 2. Efficiency vs. Output Current

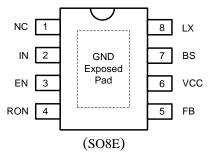

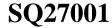

# Pinout (top view)

Top Mark: **DUF**xyz (Device code: DUF; x=year code, y=week code, z= lot number code)

| Pin Name | Pin Number  | Pin Description                                                                                                                                                                                                   |  |  |

|----------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NC       | 1           | Not connected.                                                                                                                                                                                                    |  |  |

| IN       | 2           | Input pin. Decouple this pin to GND with a low ESR ceramic capacitor.                                                                                                                                             |  |  |

| EN       | 3           | Enable control pin. This pin can also be used for programming $V_{\rm IN}$ turn on voltage with the resistor divider. The device has an accurate 1.225V rising threshold.                                         |  |  |

| RON      | 4           | Connect a resistor from this pin to the IN to set the top switch ON time. The switching frequency can be calculated using the following equation: $f_s(kHz) = \frac{11 \times V_{OUT}(V) + 500}{R_{ON}(M\Omega)}$ |  |  |

| FB       | 5           | Output feedback pin. Connect this pin to the center point of the output resistor divider (as shown in Figure 1) to program the output voltage: $V_{OUT}=1.225\times(1+R_1/R_2)$                                   |  |  |

| VCC      | 6           | Supply input of internal LDO.                                                                                                                                                                                     |  |  |

| BS       | 7           | Boot-Strap Pin. Supply high side gate driver. Decouple this pin to LX pin with 0.1uF ceramic capacitor.                                                                                                           |  |  |

| LX       | 8           | Inductor pin. Connect this pin to the switching node of inductor                                                                                                                                                  |  |  |

| GND      | Exposed Pad | Ground pin.                                                                                                                                                                                                       |  |  |

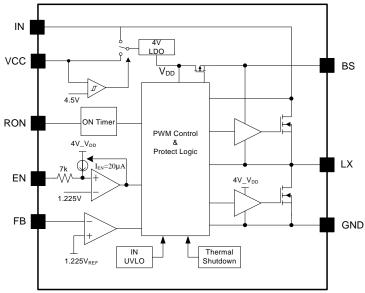

# **Block Diagram**

Figure 3. Block Diagram

| Absolute Maximum Ratings (Note 1)                     |                       |

|-------------------------------------------------------|-----------------------|

| IN                                                    |                       |

| EN, RON, LX                                           |                       |

| BS-LX                                                 |                       |

| FB Voltage                                            |                       |

| VCC                                                   |                       |

| Power Dissipation, $P_D$ @ $T_A = 25^{\circ}C$ , SO8E | 3.3W                  |

| Package Thermal Resistance (Note 2)                   |                       |

| heta JA                                               | 30°C/W                |

| θ <sup>JC</sup>                                       | 10°C/W                |

| Junction Temperature Range                            |                       |

| Lead Temperature (Soldering, 10 sec.)                 |                       |

| Storage Temperature Range                             |                       |

| Dynamic LX voltage in 50ns Duration                   | $V_{IN}+3V$ to GND-5V |

| Recommended Operating Conditions (Note 3)             |                       |

| Supply Input Voltage                                  |                       |

| Junction Temperature Range                            |                       |

| Ambient Temperature Range                             | 40°C to 85°C          |

#### **Electrical Characteristics**

$(V_{IN}=48V, V_{OUT}=5V, L=33\mu H, C_{OUT}=10\mu F, I_{OUT}=1A unless otherwise specified. Typical value correspond to$ T<sub>J</sub>=25°C. Minimum and maximum limits apply over -40°C to 125°C junction temperature range.)

| Parameter                          | Symbol                  | Test Conditions                    | Min   | Тур   | Max   | Unit      |

|------------------------------------|-------------------------|------------------------------------|-------|-------|-------|-----------|

| Input Voltage Range                | V <sub>IN</sub>         |                                    | 7     |       | 100   | V         |

| Input UVLO Rising Threshold        | V <sub>IN,UVLO</sub>    |                                    | 5.8   | 6.3   | 6.8   | V         |

| Input UVLO Hysteresis              | $V_{HYS}$               |                                    |       | 0.25  |       | V         |

| Shutdown Current                   | $I_{SHDN}$              | EN=0                               |       | 8     | 30    | μA        |

| Feedback Reference Voltage         | $V_{REF}$               |                                    | 1.2   | 1.225 | 1.25  | V         |

| FB Input Current                   | $I_{FB}$                | $V_{FB}=3.3V$                      | -100  |       | 100   | nA        |

| Top FET RON                        | R <sub>DS(ON)1</sub>    |                                    |       | 500   |       | $m\Omega$ |

| Bottom FET RON                     | R <sub>DS(ON)2</sub>    |                                    |       | 240   |       | $m\Omega$ |

| Top FET peak Current Limit         | $I_{LIM,TOP}$           |                                    | 1.4   |       | 2.2   | A         |

| Bottom FET Valley Current Limit    | I <sub>LIM,BOTTOM</sub> |                                    | 1     |       |       | A         |

| Negative Current Limit             | I <sub>LIM,NEG</sub>    |                                    |       | -1.5  |       | A         |

| VCC Input Rising UVLO<br>Threshold | V <sub>VCC,UVLO</sub>   |                                    |       | 4.5   |       | V         |

| VCC Input UVLO Hysteresis          | $V_{VCC,HYS}$           |                                    |       | 0.3   |       | V         |

| EN Rising Threshold                | $V_{EN}$                |                                    | 1.185 | 1.225 | 1.265 | V         |

| EN Hysteresis Input Current        | I <sub>EN, HYS</sub>    |                                    | -10   | -20   | -29   | μΑ        |

| Switching Frequency                | $f_{OSC}$               | $V_{IN}=48V$ , $R_{ON}=1.1M\Omega$ | 350   | 500   | 650   | kHz       |

| Min ON Time                        | t <sub>ON</sub>         | ·                                  |       | 90    |       | ns        |

| Min OFF Time                       | t <sub>OFF</sub>        |                                    |       | 200   |       | ns        |

| Thermal Shutdown Temperature       | $T_{SD}$                |                                    |       | 150   |       | °C        |

| Thermal Shutdown Hysteresis        | $T_{HYS}$               |                                    |       | 15    |       | °C        |

Note 1: Stresses beyond the "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only. Functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

Note 2:  $\theta_{JA}$  is measured in the natural convection at  $T_A = 25^{\circ}$ C on a low effective 4-layer thermal conductivity test board of JEDEC 51-3 thermal measurement standard. Paddle of SO8E package is the case position for  $\theta$   $_{

m JC}$ measurement.

**Note 3:** The device is not guaranteed to function outside its operating conditions.

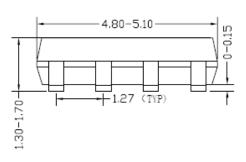

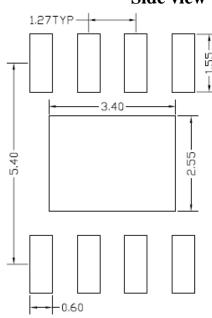

# **SO8E Package Outline & PCB layout**

Top view

**Side view**

Front view

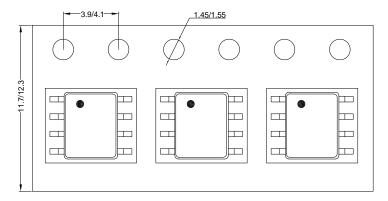

Recommended PCB layout (Reference Only)

**Notes:** All dimension in millimeter and exclude mold flash & metal burr.

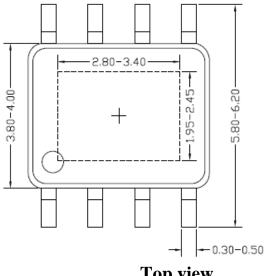

# **Taping & Reel Specification**

## 1. Taping orientation

SO8E

Feeding direction ----

### 2. Carrier Tape & Reel specification for packages

| Package<br>type | Tape width (mm) | Pocket<br>pitch(mm) | Reel size<br>(Inch) | Trailer<br>length(mm) | Leader length<br>(mm) | Qty per<br>reel |

|-----------------|-----------------|---------------------|---------------------|-----------------------|-----------------------|-----------------|

| SO8E            | 12              | 8                   | 13"                 | 400                   | 400                   | 2500            |

#### 3. Others: NA

# 单击下面可查看定价,库存,交付和生命周期等信息

>>SILERGY(矽力杰)