# ISG3201

## 1. Features

- 2x 100V, 3.2mohm Emode GaN HEMT with Half Bridge Driver

- · 60A continuous current capability

- · Zero reverse recovery charge

- · Ultra-low on resistance

- Minimum external components. (Driving resistor, bootstrap and Vcc capacitors integrated)

- Reduced Gate Loop Inductance.

- · Reduced Power Loop Inductance.

- · Easy for power stage layout.

- Independent High-Side and Low-Side TTL Logic Inputs

- High-side floating bias voltage rail operates up to 100 VDC

- · Fast Propagation Times (17ns Typical)

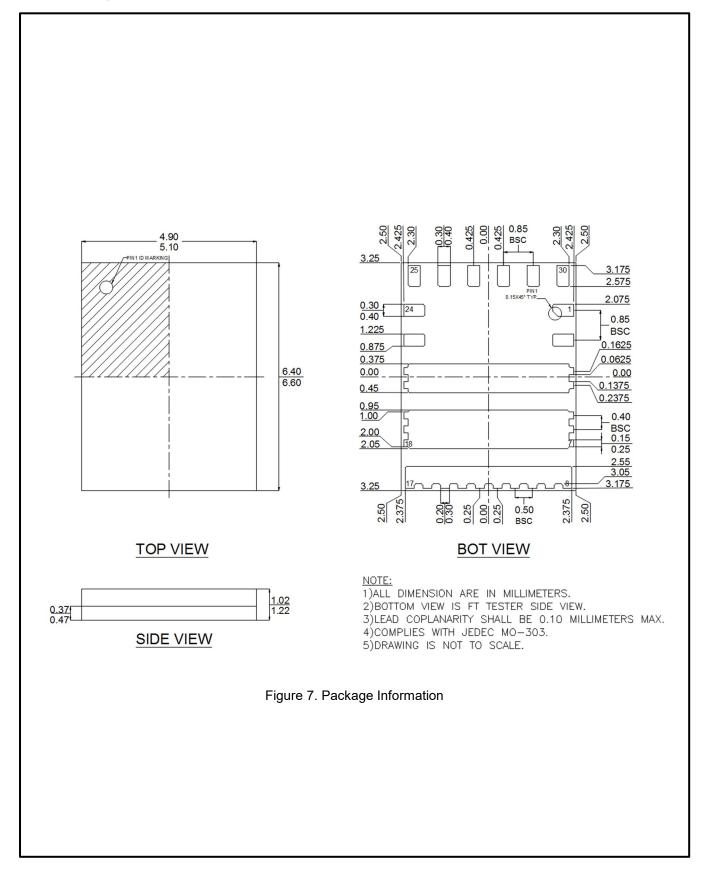

- 5mmx6.5mmx1.12mm LGA Package

# 2. Applications

ISG3201 is suitable for high-frequency Buck converter, half bridge or full bridge converters, Class D audio amplifier, LLC converter and power modules in the following applications:

- Al

- · Server

- · Telecom

- Super Computer

- Motor Drive

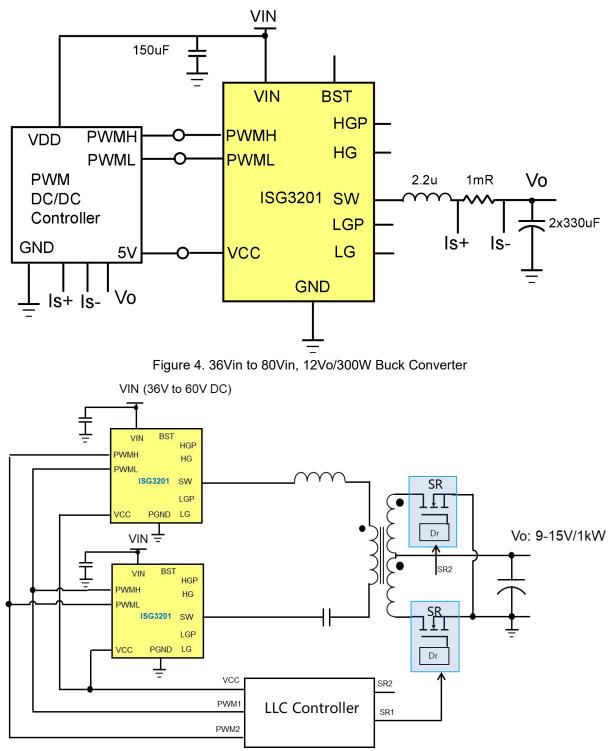

# 4. Typical Application

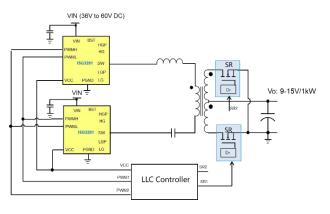

#### 36V-60V Vin, 4:1 Non-regulated LLC Converter

## 3. General description

The ISG3201 is a 100V Copak product in Innoscience's SolidGaN family. It integrates two 100V enhancement mode GaN devices with a 100V half-bridge gate driver. ISG3201 employs bootstrap technique for high-side driver voltage and can operate up to 100V. The integrated driver eliminates the external clamping circuit. Besides, turn-on and turn-off resistors, bootstrap and VCC decoupling caps are all integrated which makes the external circuit super simple. Due to excellent internal layout, the associated gate loop and power loop parasitic is reduced significantly, with value much less than 1nH. As a result, ultra-low voltage spike on switch nodes can be achieved. Turn-on speed of the half-bridge GaN HEMTs can be adjusted by an optional resister. The optimized pin layout of ISG3201 optimizes the power flow and simplifies the PCB board layout. ISG3201 employs independent high-side and low-side PWM input, which are usually available from most of GaN controllers. ISG3201 The available is in а compact 5mmx6.5mmx1.12mm LGA package.

## **POWER THE FUTURE**

## 5. Absolute maximum ratings

at Tj = 25 °C unless otherwise specified.

All voltages are with respect to PGND pin.

Exceeding the maximum ratings may destroy the device. For further information, contact Innoscience sales office.

| SYMBOL                  | PARAMETER                                   | MAX                     | UNIT |

|-------------------------|---------------------------------------------|-------------------------|------|

| V <sub>DS</sub>         | Drain-to-Source Voltage (Continuous)        | 100                     | V    |

| Vin                     | Input Voltage Supply, Vin to GND            | 100                     | V    |

| I                       | Continuous current for internal GaN HEMT    | 60 (*)                  | A    |

| Ι <sub>D</sub>          | Pulsed (25°C, T <sub>Pulse</sub> = 100 μs)  | 230                     | A    |

| TJ                      | Operating Temperature                       | -40 to 150              | °C   |

| T <sub>STG</sub>        | Storage Temperature                         | -40 to 150              | °C   |

| V <sub>CC(DC)</sub>     | Supply Voltage (DC)                         | -0.3 to 6.0             | V    |

| V <sub>CC(25ns)</sub>   | V <sub>CC(25ns)</sub> Supply Voltage (25ns) |                         | V    |

| V <sub>BST-SW(DC)</sub> | BST to SW Voltage (DC)                      | -0.3 to 6.0             | V    |

| VBST-SW(25ns)           | BST to SW Voltage (25ns)                    | -0.3 to 8.0             | V    |

| V <sub>SW(DC)</sub>     | V <sub>SW(DC)</sub> SW pin Voltage          |                         | V    |

| V <sub>SW(25ns)</sub>   | SW pin Voltage (25ns)                       | -5V to 108              | V    |

| VBST-PGND               | BST to PGND Voltage                         | -0.3 to Vsw+6.0         | V    |

|                         | HCD HC nin Voltage                          | V <sub>SW</sub> -0.3 to | V    |

| $V_{HGP}, V_{HG}$       | HGP, HG pin Voltage                         | V <sub>BST</sub> +0.3   |      |

| $V_{LGP}, V_{LG}$       | LGP, LG pin Voltage                         | -0.3 to 6.0             | V    |

| PWMH,<br>PWML           | PWMH, PWML pin Voltage                      | -0.3 to 6.0             | V    |

Table 1 Absolute maximum ratings at  $T_i = 25 \ ^{\circ}C$

(\*) Ideal thermal condition. In real application the current capability depends on system thermal design.

## 6. Recommended Operating Conditions

#### Table 2 Recommended operating Conditions

| Parameter                                     | Min    | Max    | Unit |

|-----------------------------------------------|--------|--------|------|

| Vin                                           |        | 80     | V    |

| VCC                                           | 4.5    | 5.5    | V    |

| PWMH, PWML                                    | 0      | 5.5    | V    |

| Vsw                                           | -4     | 100    | V    |

| BST                                           | SW+4.5 | SW+5.5 | V    |

| SW Slew Rate                                  |        | 50     | V/ns |

| Operating Junction Temperature T <sub>J</sub> | -40    | 125    | °C   |

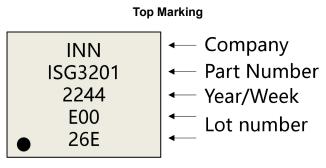

## 7. Ordering information

#### Table 3 Ordering information

| PART NUMBER | PAD FINISH <sup>1</sup><br>(Note 1) | TOP MARKING | PACKAGE<br>TYPE | MSL<br>RATING |

|-------------|-------------------------------------|-------------|-----------------|---------------|

| ISG3201     | SAC305 (RoHS)                       | See Below   | LGA             | 3             |

Page 2

1. Pad or ball finish code is per IPC/JEDEC J-STD-609.

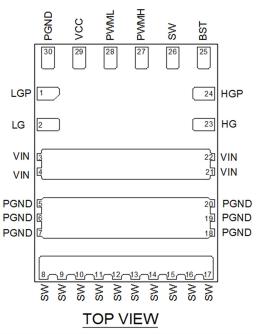

## 8. Pinout description

Package top view is shown as follows:

| Pin<br>Number    | Symbol | Pin Type | Description                                                                                                                                                                                |

|------------------|--------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                | LGP    | Output   | Low side gate driver source-current output. An optional resistor between LGP<br>and LG can be employed to adjust turn-on speed of low side GaN HEMT. See<br>in Apps info for more details. |

| 2                | LG     | Output   | Low side gate terminal.                                                                                                                                                                    |

| 3-4,21-22        | VIN    | Power    | Input voltage supply. Add high quality decoupling cap between VIN and PGND with minimum loop.                                                                                              |

| 5-7,18-20,<br>30 | PGND   | GND      | Power ground.                                                                                                                                                                              |

| 8-17             | SW     | Output   | Switching node.                                                                                                                                                                            |

| 23               | HG     | Output   | High side gate terminal.                                                                                                                                                                   |

| 24               | HGP    | Output   | High side gate driver source-current output. An optional resistor between HGP and HG can be employed to adjust turn-on speed of high side GaN                                              |

Page 3

## **POWER THE FUTURE**

Downloaded From Oneyac.com

## **ISG3201** 100V Half-Bridge Solid-GaN Integrating Gate Driver

# Innoscience

|    |               |        | HEMT. See in apps info for more details.                                          |

|----|---------------|--------|-----------------------------------------------------------------------------------|

| 25 | 25 BST Output |        | High side gate driver bootstrap rail, bootstrap cap is built in internally and no |

| 23 | 001           | Output | decoupling cap is required between BST and SW pin.                                |

| 26 | SW            | Output | Switching node. SW waveform can be monitored.                                     |

| 27 | PWMH          | Input  | High side driver PWM input. Can be floating if not used.                          |

| 28 | PWML          | Input  | Low side driver PWM input. Can be floating if not used.                           |

| 29 | VCC           | Input  | External 5V Driver supply. No decoupling cap to PGND is required.                 |

Page 4

#### **POWER THE FUTURE**

# 9. Electrical specification

$V_{CC}$  =5V,  $T_A$  = 25°C for typical value, unless otherwise noted. For further information, contact Innoscience sales office.

#### Table 5Electrical specification

| Parameter                             | Symbol                | Min.     | Тур.       | Max.        | Units               | Note/Test Condition              |

|---------------------------------------|-----------------------|----------|------------|-------------|---------------------|----------------------------------|

|                                       |                       |          | VCC S      |             | <b>I</b>            |                                  |

| Ivcc Quiescent Current                |                       |          |            | 100         | uA                  | PWMH=PWML=0                      |

| Ivcc Operation Current                |                       |          |            | 30          | mA                  |                                  |

| V <sub>cc</sub> Under Voltage Lockout | VCCVTH                |          | 4          | 4.25        | V                   |                                  |

| Threshold Rising                      | VCCVTH                |          | 4          | 4.35        | V                   |                                  |

| V <sub>CC</sub> Under Voltage Lockout | VCC <sub>HYS</sub>    |          | 300        |             | mV                  |                                  |

| Threshold Hysteresis                  | VCCHYS                |          | 500        |             | IIIV                |                                  |

|                                       |                       |          | PWM INF    | PUT         |                     |                                  |

| PWM Logic High Voltage                | V <sub>H_PWM</sub>    | 2.1      |            |             | V                   |                                  |

| PWM Threshold Hysteresis              | V <sub>HYS_PWM</sub>  |          | 400        |             | mV                  |                                  |

| PWM Logic Low Voltage                 | V <sub>L_PWM</sub>    |          |            | 1.3         | V                   |                                  |

| PWM input pull-down resistance        | R <sub>PWM_IN</sub>   |          | 200        |             | kΩ                  |                                  |

|                                       |                       | High and | d Low-side | e Gate Driv | /er                 |                                  |

| Peak source current (*)               | ISOURCE               |          | 1.7        |             | A                   | $V_{HG-SW}=0V, V_{LG-LS}=0V$     |

| Peak sink current (*)                 | Isink                 |          | 5.2        |             | A                   | $V_{HG-SW}$ =5V, $V_{LG-LS}$ =5V |

| Source Resistance                     | RSOURCE               |          | 1.3        |             | Ω                   | I <sub>SOURCE</sub> =100mA, 5V   |

| Sink Resistance                       | Rsink                 |          | 0.2        |             | Ω                   | I <sub>SINK</sub> =100mA, 5V     |

|                                       | High and Lo           | w-side G | ate Driver | Timing Ch   | aracteristics       | (*)                              |

| HGP Rise Time (0.5V-4.5V)             | T <sub>R_SW</sub>     |          | 10         |             | ns                  | 3.3nF load, VCC=5V               |

| HG Fall Time (4.5V-0V)                | T <sub>F_SW</sub>     |          | 3          |             | ns                  | 3.3nF load, VCC=5V               |

| LGP Rise Time (0.5V-4.5V)             | T <sub>R_LS</sub>     |          | 10         |             | ns                  | 3.3nF load, VCC=5V               |

| LG Fall Time (4.5V-0.5V)              | T <sub>F_LS</sub>     |          | 3          |             | ns                  | 3.3nF load, VCC=5V               |

| HGP Turn-On propagation               | +                     |          | 17         |             | <b>n</b> 0          | 3.3nF load, VCC=5V,              |

| Delay                                 | t <sub>HPH</sub>      |          | 17         |             | ns                  | PWMH rising to HGP rising        |

| HG Turn-Off propagation               | +                     |          | 17         |             | <b>no</b>           | 3.3nF load, VCC=5V,              |

| Delay                                 | t <sub>HPL</sub>      |          | 17         |             | ns                  | PWMH rising to HGP rising        |

| LGP Turn-On propagation Delay         | t                     |          | 17         |             | nc                  | 3.3nF load, VCC=5V,              |

| LGF Turn-On propagation Delay         | t <sub>LPH</sub>      |          | 17         |             | ns                  | PWMH rising to HGP rising        |

| LG Turn-Off propagation               | )ff propagation       | 17       | 7          | ne          | 3.3nF load, VCC=5V, |                                  |

| Delay                                 | t <sub>LPL</sub>      |          |            |             | ns                  | PWML falling to LG falling       |

| LGP on & HG off delay                 | torry                 |          | 1.5        |             | ns                  |                                  |

| matching                              | t <sub>OFF_M</sub>    |          | 1.5        |             | 113                 |                                  |

| LG off & HGP on delay                 | tour                  |          | 1.5        |             | ne                  |                                  |

| matching                              | t <sub>on_M</sub>     |          | 1.5        |             | ns                  |                                  |

| Minimal input PWM pulse               | tpwm_min              |          | 10         |             | ns                  |                                  |

| Minimal gate output pulse             | t <sub>GATE_MIN</sub> |          | 13         |             | ns                  |                                  |

|                                       |                       |          | GaN FE     | ET          |                     |                                  |

| Drain-to-Source Voltage               | BV <sub>DSS</sub>     | 100      |            |             | V                   | $V_{GS} = 0 V, I_D = 400 \mu A$  |

Page 5

## **POWER THE FUTURE**

Downloaded From Oneyac.com

## **ISG3201** 100V Half-Bridge Solid-GaN Integrating Gate Driver

# Innoscience

|                                |                             |     | 1    | 1    |      |                                               |

|--------------------------------|-----------------------------|-----|------|------|------|-----------------------------------------------|

| Drain-Source Leakage           | I <sub>DSS</sub>            |     | 80   | 350  | μA   | V <sub>GS</sub> = 0 V, V <sub>DS</sub> = 80 V |

| Gate-to-Source Forward         |                             |     | 20   | 5000 |      | $V_{GS} = 5 V$                                |

| Leakage(25°C)                  |                             |     | 20   | 5000 | μA   | V <sub>GS</sub> – 5 V                         |

| Gate-to-Source Forward         | I <sub>GSS</sub>            |     | 0.6  | 9    | mA   | V <sub>GS</sub> = 5 V                         |

| Leakage(125°C)                 |                             |     | 0.0  | 9    | IIIA | VGS – 5 V                                     |

| Gate-to-Source Reverse Leakage |                             |     | 60   | 400  | μA   | V <sub>GS</sub> = -4 V                        |

| Gate Threshold Voltage         | V <sub>GS(TH)</sub>         | 0.8 | 1.1  | 2.5  | V    | $V_{DS} = V_{GS}$ , $I_D = 9 \text{ mA}$      |

| Drain-Source On Resistance     | R <sub>DS(on)</sub>         |     | 2.4  | 3.2  | mΩ   | V <sub>GS</sub> = 5 V, I <sub>D</sub> = 25 A  |

| Source-Drain Forward Voltage   | Vsd                         |     | 1.5  |      | V    | I <sub>S</sub> = 0.5 A, V <sub>GS</sub> = 0 V |

| Input Capacitance              | CISS                        |     | 1000 |      |      | $V_{GS}$ = 0 V, $V_{DS}$ = 50 V               |

| Output Capacitance             | Coss                        |     | 460  |      |      | V <sub>GS</sub> = 0 V, V <sub>DS</sub> = 50 V |

| Reverse Transfer Capacitance   | C <sub>RSS</sub>            |     | 8.2  |      | pF   | V <sub>GS</sub> = 0 V, V <sub>DS</sub> = 50 V |

| Energy Related Coss            | $C_{\text{OSS(ER)}}$        |     | 700  |      |      | $V_{GS}$ = 0 V, $V_{DS}$ = 0 to 50 V          |

| Time Related Coss              | $C_{\text{OSS}(\text{TR})}$ |     | 1020 |      |      | $V_{GS}$ = 0 V, $V_{DS}$ = 0 to 50 V          |

| Gate resistance                | R <sub>G</sub>              |     | 2.2  |      | Ω    |                                               |

| Total Gate Charge              | $Q_{G}$                     |     | 9.2  | 12   |      | $V_{GS}$ = 5 V, $V_{DS}$ =50V, $I_{D}$ = 25 A |

| Gate-to-Source Charge          | Q <sub>GS</sub>             |     | 1.9  |      |      | $V_{DS}$ = 0V to 50 V, $I_D$ = 25 A           |

| Gate-to-Drain Charge           | $Q_{GD}$                    |     | 1.7  |      | nC   | $V_{DS}$ = 0V to 50V, $I_D$ = 25 A            |

| Gate Charge at Threshold       | Q <sub>G(TH)</sub>          |     | 1.1  |      |      | $V_{DS}$ = 0V to 50V, $I_D$ = 25 A            |

| Output Charge                  | Q <sub>oss</sub>            |     | 50   |      |      | $V_{GS} = 0 V, V_{DS} = 0 to 50V$             |

(\*) Guaranteed by design or characterization data, not tested in production.

## **10. Thermal characteristics**

#### Table 6 Thermal characteristics

| Parameter                                   | Symbol                | Values | Unit | Note/Test Condition          |                              |

|---------------------------------------------|-----------------------|--------|------|------------------------------|------------------------------|

| Thermal resistance, junction to case Top    | D                     | 27     | °C/W | Determined by simulation per |                              |

|                                             | R <sub>thJC-TOP</sub> |        |      | JESD51 conditions            |                              |

| Thermal resistance, junction to case Bottom | R <sub>thJC-BOT</sub> | 7.7    | °C/W | Determined by simulation per |                              |

|                                             |                       |        |      | JESD51 conditions            |                              |

| Thermal registeres, junction to embient     |                       | 40     |      | °C/W                         | Determined by simulation per |

| Thermal resistance, junction to ambient     | R <sub>thJA</sub>     | 48     | C/vv | JESD51 conditions            |                              |

| Reflow soldering temperature                | T <sub>sold</sub>     | ≤260   | °C   |                              |                              |

\*According to standards defined in JESD51 and JESD51-1, thermal characteristic of the package is simulated.

# 11. ESD ratings

#### Table 7 ESD ratings

| Parameter                               | Symbol | Values | Unit | Note/Test Condition  |

|-----------------------------------------|--------|--------|------|----------------------|

| Human Rody Model (per JESD22 A114)      | НВМ    | ±1000  | V    | Human Body Model     |

| Human Body Model (per JESD22-A114)      |        |        | v    | (per JESD22-A114)    |

| Charged Device Medel (per JESD22 C101E) | СДМ    | + 500  | V    | Charged Device Model |

| Charged Device Model (per JESD22-C101F) | CDM    | ±500   | v    | (per JESD22-C101F)   |

Page 6

# **12. Typical Performance Characteristics**

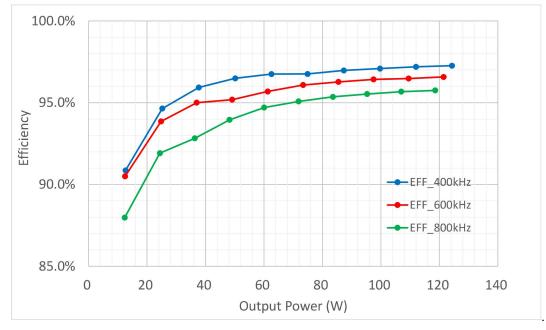

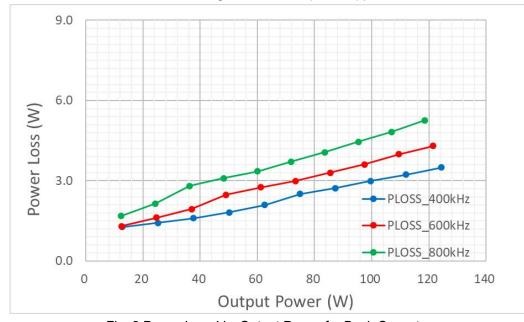

Fig. 1 Typical Efficiency Vs. Output Power for Buck Converter

Buck Converter: Vin=48V, Vo=12V,  $R_{gon}=5\Omega$ ,  $R_{goff}=0\Omega$ .  $T_{dead}=10$ ns. L=2.2uH/0.7m $\Omega$ . Based on Inno Demo Board: INNEHB100B1. Refer to Figure 4 for a simplified application schematic.

INNEHB100B1. Refer to Figure 4 for a simplified application schematic.

Page 7

## **POWER THE FUTURE**

www.innoscience.com

Downloaded From Oneyac.com

Datasheet Rev. 1.0 2023/06/28

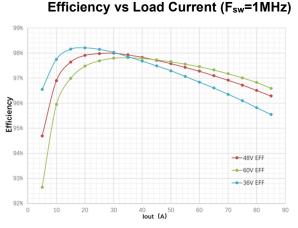

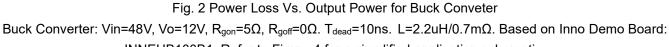

Fig. 3 Typical Efficiency Vs. Output Current for LLC Converter LLC Converter: 4:1 Non-regulated, R<sub>gon</sub>=4Ω, F<sub>sw</sub>=1MHz, L<sub>p</sub>=3.4uH. T<sub>dead</sub>=53ns. Cr=3100nF. Based on Inno Demo Board: INNDDD1K0A1. Refer to Figure 5 as a simplified application schematic.

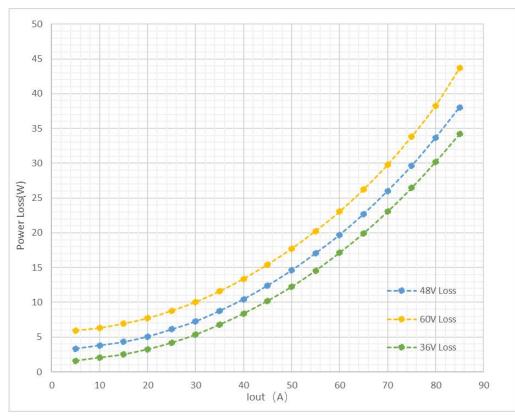

Fig. 4 Power Loss Vs. Output Current for LLC Converter

LLC Converter: 4:1 Non-regulated, R<sub>gon</sub>=4Ω, F<sub>sw</sub>=1MHz, L<sub>p</sub>=3.4uH. T<sub>dead</sub>=53ns. Cr=3100nF. Based on Inno Demo Board: INNDDD1K0A1. Refer to Figure 5 as a simplified application schematic.

Page 8

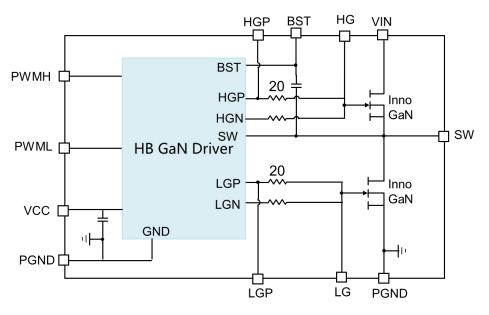

# 13. Block Diagram

Block Diagram of ISG3201 is shown as Figure 1. A half-bridge GaN driver and two 100V GaN HEMTs are integrated. Besides, Vcc decoupling capacitor, Bootstrap capacitor, internal  $20\Omega$  turn-on resister for both GaN HEMTs are also integrated. Turn-on speed can be adjusted by an optional resistor between HGP(LGP) pin and HG(LG) pin for top (bottom) GaN HEMT.

Figure 1. Block diagram of ISG3201

# 14. Operation and Applications Information

The ISG3201 is designed as a fully integrated GaN Half-bridge power stages for multiple applications in Data Center, Server, Super computer, motor drive and class D audio systems. It is one of leading products in Innoscience's SolidGaN families. ISG3201 is small-footprint, easy for design and layout and serve as "drop-in" solution for board power. ISG3201 combines world-class GaN performance from Innoscience with high performance half-bridge driver specifically designed for GaN. Bootstrap capacitor, driving resistors and Vcc decoupling caps are all integrated into ISG3201 which significantly simplifies the application circuit. The optimized pinout structure makes the layout ultra easy while the parasitic is reduced significantly, i.e. gate loop and power loop paracitics. As a result, voltage spike of SW node is very small which enhances the reliability of the system.

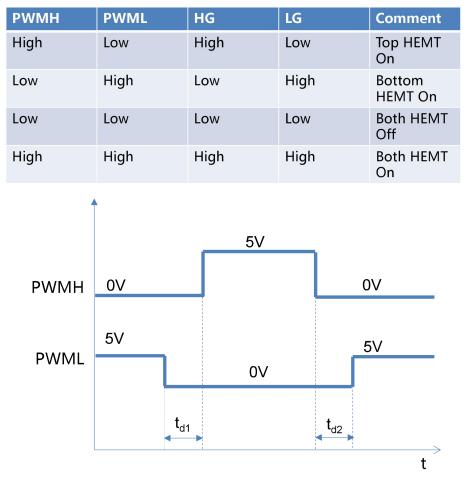

## 14.1 PWM Input and Output

The PWMH and PWML are logical inputs which can with stand voltage up to 5.5V and independently controlled. PWMH controls the high-side FETs and PWML controls low-side FETs of the same bridge. Please refer to Table 8 as below. Therefore, the users must avoid shoot through by setting sufficient dead time,  $t_{d1}$  and  $t_{d2}$ , between PWMH and PWML, as illustrated in Figure 2.

Page 9

## **POWER THE FUTURE**

#### Table 8: PWMH and PWML True Table

Figure 2. Dead-time Illustration diagram

ISG3201 employs a gate driver which separate the gate turn-on and turn-off outputs. A default internal  $20\Omega$  turn-on resister for both GaN HEMTs are integrated. Turn-on speed can be increased by an optional resistor between HGP(LGP) pin and HG(LG) pin for top (bottom) GaN HEMT. The total effective resistance is the parallel of the external resistor and  $20\Omega$ internal resistor.

#### 14.2 UVLO Protection

When VCC voltage is lower than the threshold voltage of VCC<sub>VTH</sub>, both PWMH and PWML are ignored. When VCC>VCC<sub>VTH</sub> both HG and LG are working. Please refer to Table 8.

#### 14.3 BOOTSTRAP Clamping inside ISG3201

Due to the intrinsic feature of enhancement mode GaN FETs, the source-to-drain voltage of the bottom switch, is usually higher than a diode forward voltage drop when the gate is pulled low. For example, When  $V_{gs}$ =0V and the source to drain current is 15A, source-to-drain voltage is around 1.5V. This will cause negative voltage on SW pin. Moreover, this negative voltage transient will be even worse, considering layout and device drain /source parasitic inductances. With high side driver using the floating bootstrap configuration, negative SW voltage can lead to an excessive bootstrap voltage which can damage the high-side GaN FET. ISG3201 employ new charging logical, only when PWML=1, the BST-SW voltage will be charged from VCC. There is no current path from VCC to BST when

PWML=0, so the BST-SW voltage should <=VCC. Besides, an active circuit clamps BST-SW voltage from exceeding (1.05\*VCC).

An internal bootstrap cap is already integrated into ISG3201. Additional bootstrap cap can also been added between BST and SW pin, if necessary. To ensure reliable operation of bootstrap cap charging, the pulse width of PWML=1 should be larger than 50ns.

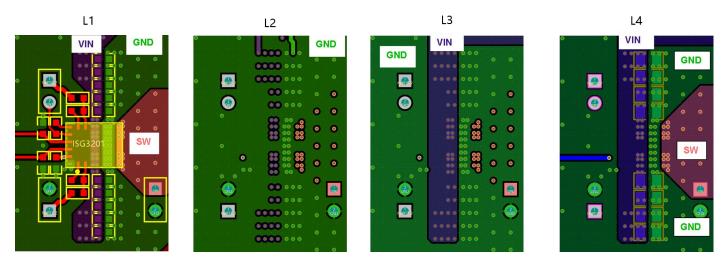

#### 14.4 Layout Recommendation

The GaN HEMTs feature very small input capacitance: i.e. a very small gate capacitance and miller capacitance. Therefore, The GaN HEMTs can operate with very-fast-speed switching: i.e. high dv/dt and high di/dt. In order to avoid the voltage and current spike caused by high dv/dt and high di/dt, the parasitic of the gate driving loop and power loop must be reduced by proper layout technique.

ISG3201 employs an excellent layout on internal substrate to reduce the gate driving loop and power loop: (1) the driver has been placed very close to the GaN HEMTs to minimize the loops of parasitic inductance and reduce the noise on the gate loop. (2) the bootstrap capacitor is integrated in the module and the distance between BST and VCC to the driver has been minimized which avoids the possible high peak current during recharging time. (3) the distance between high-side GaN FET and low-side GaN FET has been minimized to avoid excessive negative voltage to the driver caused by the parasitic inductance between high-side GaN HEMT.

Although the optimized pinout of ISG3201 simplifies the power stage layout significantly, to fully utilize the benefit of ISG3201, A good power board layout is still necessary.

The layout guidelines are as follows:

1. The optional resistor between HGP(LGP) pin and HG(LG) pin to adjust the turn-on speed of the GaN HEMT should be placed close to ISG3201.

2. The optional VCC decoupling capacitor should be placed close to ISG3201.

3. The power input decoupling caps should be placed close to Vin bar and PGND bar. One 4-layer layout example is shown as Figure 3. 2-layer board design is also possible thanks to the optimized ISG3201 pinout.

Figure 3. 4-Layer Layout Example

Page 11

## **POWER THE FUTURE**

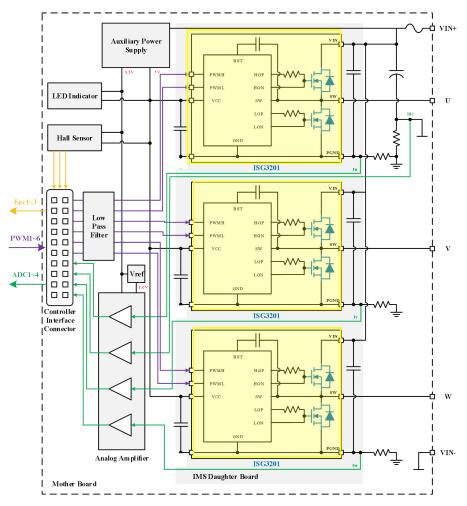

The typical ISG3201 application circuit is shown in Figure 4 for Buck converter, Figure 5 for LLC converter, and Figure 6 for 500W continuous/1000W pulsed power capability motor driver.

Figure 5. 36V-60V Vin, 9V-15V Vo /1kW LLC Resonant Converter

Page 12

## **POWER THE FUTURE**

Figure 6. 500W Continuous/1000W Pulse Power Capability Motor Driver

Page 13

#### **POWER THE FUTURE**

Innoscience

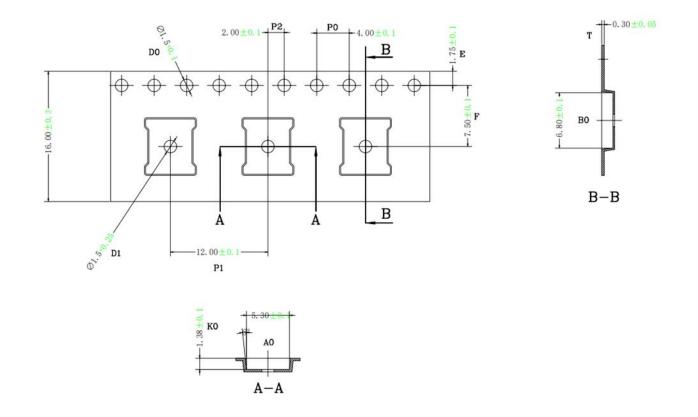

# 15. Package Information

Page 14

#### **POWER THE FUTURE**

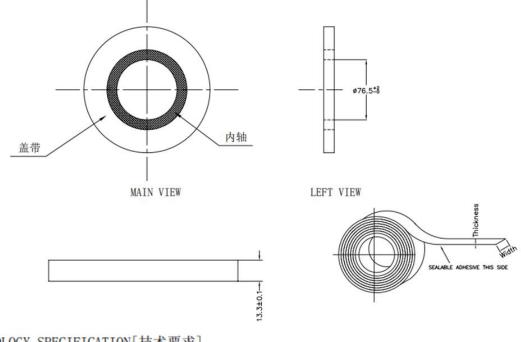

## 16. Tape and Reel Information

TECHNOLOGY SPECIFICATION [技术要求]

- 1. COVER TAPE COLOR: TRANSPARENT. [盖带颜色:透明]

- 2. COVER TAPE THICKNESS: 48±5um. [盖带厚度: 48±5微米]

- 3. THE MATERIAL: PS[材质: 聚乙烯]

- 4. SURFACE RESISTANCE: 1×10<sup>5</sup>~1×10<sup>11</sup>Ω. [表面电阻: 1×10<sup>5</sup>~1×10<sup>11</sup>Ω]

- 5. BAN TO USE THE LEVEL 1 ENVIRONMENT-RELATED SUBSTANCES OF JCET PRESCRIBING.

[禁止使用长电科技规定的一级环境管理物质]

Figure 8. Tape Information

Page 15

## **POWER THE FUTURE**

TECHNOLOGY SPECIFICATION [技术要求]

- 1. CARRIER TAPE COLOR: BLACK. [载带颜色为黑色]

- 2. THE MATERIAL: PS [材质: 聚苯乙烯]

- 3. SURFACE RESISTANCE 1X10<sup>4</sup>~1X10<sup>9</sup>OHMS. [表面电阻为1X10<sup>4</sup>~1X10<sup>9</sup>Ω]

- 4. MOLD# LGA (5×6.5). [载带规格LGA (5×6.5)]

- 5. COVER TAPE WIDTH: 13. 3±0. 1mm. [配套13. 3±0. 1mm宽盖带]

- 6. TOLERANCE: X. X ±0.20 X. XX±0.10 [未注明公差参考: X. X±0.2 X. XX±0.10]

- 7. COVER TAPE COLOR: TRANSPARENT [盖带颜色无色透明]

- 8. BAN TO USE THE LEVEL 1 ENVIRONMENT-RELATED SUBSTANCES OF JCET PRESCRIBING. [禁止使用长电科技规定的一级环境管理物质]

Figure 9. Reel Information

Page 16

#### **POWER THE FUTURE**

www.innoscience.com

Downloaded From Oneyac.com

Datasheet Rev. 1.0 2023/06/28

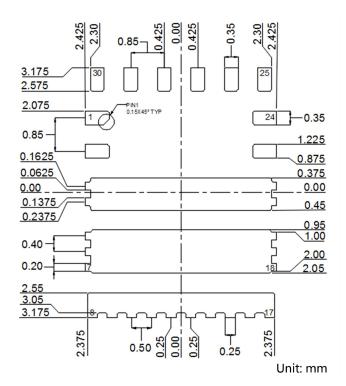

# 17. Recommended Land Pattern.

Figure 10. Recommended Land Pattern

## **18. Revision History**

#### Major changes since the last revision

| Revision | Date       | Description of changes                      |

|----------|------------|---------------------------------------------|

| DS 1.0   | 2023-06-28 | Final datasheet at product release – for MP |

## **Important Notice**

The information provided in this document is intended as a guide only and shall not in any event be regarded as a guarantee of conditions, characteristics or performance. Innoscience does not assume any liability arising out of the application or use of any product described herein, including but not limited to any personal injury, death, or property or environmental damage. No licenses, patent rights, or any other intellectual property rights is granted or conveyed. Innoscience reserves the right to modify without notice. All rights reserved.

Page 17

## **POWER THE FUTURE**

www.innoscience.com Downloaded From Oneyac.com Datasheet Rev. 1.0 2023/06/28 单击下面可查看定价,库存,交付和生命周期等信息

>>Innoscience(英诺赛科)