## Single-Channel GaN Driver

### 1. Features

- Wide 6V to 20V Operating Voltage Range

- Dual Inverting and Non-Inverting PWM Inputs

- Independent Pullup and Pulldown Outputs for Adjustable Turn-on and Turn-off Speeds

- · Strong 1.3- $\Omega$  Pullup and 0.5- $\Omega$  Pulldown Resistance

- Fast Propagation Delay with Input Deglitching

- User Programmable Gate Driver Supply Voltage

- Integrated 5V LDO for supplying Digital Isolator

- · Built-In UVLO, OVP, OTP Protection

## 2. Applications

- · Switch-Mode Power Supplies

- · AC-DC, DC-DC Converters

- · Boost, Flyback, and Forward Converters

- · Half-Bridge and Full-Bridge Converters

- Synchronous Rectification

- · Solar Inverters, Motor Control, UPS

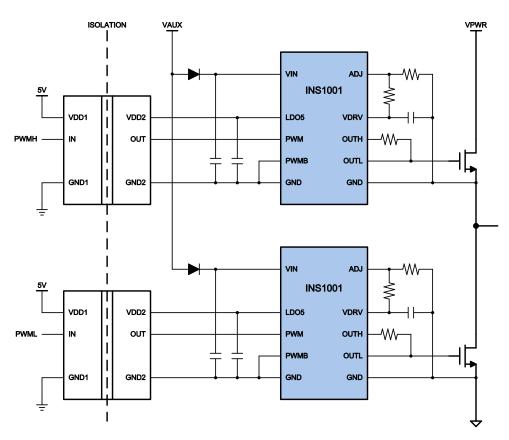

## 4. Typical Application

### 3. Description

The INS1001 is designed to drive single-channel GaN FET(s) in either low-side, high-side, or secondary-side SR applications. It has both non-inverting and inverting PWM inputs, working with controller, opto-coupler, and digital isolator flexibly. The gate driver has two separate outputs, allowing independent adjustment of turn-on and turn-off speeds. The driver voltage can be adjusted through an external resistor divider, tailoring for different gate voltage requirements of GaN FETs. Integrated 5V LDO can supply digital isolator or other circuitry in high-side applications. The strong driving capability and fast propagation delay, along with input noise deglitching and built-in UVLO, OVP, OTP protection features, make the INS1001 extremely suitable for high power, high frequency, and robust power GaN applications. The INS1001 is available in thermally enhanced DFN3x3-10L package.

Page 1

### **POWER THE FUTURE**

www.innoscience.com

DS Rev1.0 2024/01/30

## Table of contents

| 1.  | Features                         | 1   |

|-----|----------------------------------|-----|

| 2.  | Applications                     | 1   |

| 3.  | Description                      | 1   |

| 4.  | Typical Application              | 1   |

| 5.  | Revision History                 | 2   |

| 6.  | Pin Configuration and Functions  | 3   |

| 7.  | Absolute Maximum Ratings         | 4   |

| 8.  | ESD Ratings                      | 4   |

| 9.  | Recommended Operating Conditions | 4   |

| 10. | Thermal Information              | 4   |

| 11. | Electrical Characteristics       | 5   |

| 12. | Switching Characteristics        | 6   |

| 13. | Typical Characteristics          | 7   |

| 14. | Block Diagram                    | .10 |

| 15. | Function Description             | .10 |

| 16. | Package Information              | .14 |

| 17. | Tape and Reel Information        | .15 |

| 18. | Recommended Land Pattern         | .16 |

| 19. | Order Information                | .16 |

|     |                                  |     |

## 5. Revision History

#### Major changes since the last revision

| Revision | Date       | Description of changes  |

|----------|------------|-------------------------|

| 1.0      | 2024-01-30 | Final release datasheet |

Page 2

#### **POWER THE FUTURE**

www.innoscience.com

DS Rev1.0 2024/01/30

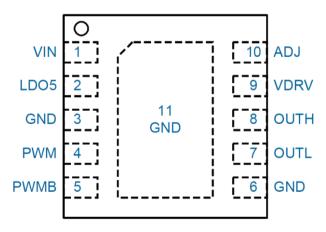

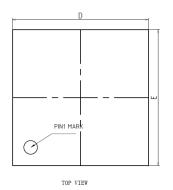

## 6. Pin Configuration and Functions

10-Lead DFN (3mm x 3mm) Package - Top View

| Pin Number | Pin Name | Description                                                                     |

|------------|----------|---------------------------------------------------------------------------------|

| 1          | VIN      | Supply Voltage Input. Locally bypass this pin to GND with a ceramic capacitor.  |

| 2          | LDO5     | 5V LDO Output. This pin provides power to internal logic circuitry and external |

| Z          | LDO3     | circuitry up to 20mA. Locally bypass this pin to GND with a ceramic capacitor.  |

| 3, 6, 11   | GND      | Ground. Internally shorted together.                                            |

| 4          | PWM      | PWM Input. Receive PWM signal from the controller.                              |

| 5          | PWMB     | Inverting PWM Input. Receive inverting PWM signal from the controller.          |

| 7          | OUTL     | Gate Driver Pulldown Output. Connect to the gate of GaN FET and use a           |

| 1          |          | resistor to adjust the turn-off speed.                                          |

| 8          | OUTH     | Gate Driver Pullup Output. Connect to the gate of GaN FET and use a resistor    |

| 0          | 0016     | to adjust the turn-on speed.                                                    |

| 9          | VDRV     | Driver Voltage Output. Regulated LDO output from VIN to supply GaN FET          |

| 9          | VDRV     | gate driver power. Locally bypass this pin to GND with a ceramic capacitor.     |

| 10         |          | Driver Voltage Adjustment. Connect a resistor divider between VDRV and          |

| 10         | ADJ      | GND to this pin to set the VDRV output voltage.                                 |

Page 3

#### **POWER THE FUTURE**

www.innoscience.com

DS Rev1.0 2024/01/30

### 7. Absolute Maximum Ratings

All pins are referred to GND, unless otherwise specified. Stress beyond the absolute maximum ratings can cause permanent damage or deteriorate device lifetime.

| Parameter                                     | Min  | Max      | Unit |

|-----------------------------------------------|------|----------|------|

| VIN                                           | -0.3 | 22       | V    |

| VDRV                                          | -0.3 | 13.2     | V    |

| OUTH, OUTL                                    | -0.3 | VDRV+0.3 | V    |

| PWM, PWMB                                     | -0.3 | 6        | V    |

| LDO5, ADJ                                     | -0.3 | 6        | V    |

| Operating Junction Temperature T <sub>J</sub> | -40  | 150      | °C   |

| Storage Temperature                           | -55  | 150      | °C   |

## 8. ESD Ratings

| Parameter                                              | Value | Unit |

|--------------------------------------------------------|-------|------|

| Human Body Model (HBM), per ANSI/ESDA/JEDEC JS-001     | ±2000 | V    |

| Charged Device Model (CDM), per ANSI/ESDA/JEDEC JS-002 | ±1000 | V    |

### 9. Recommended Operating Conditions

| Parameter                                     | Min | Max | Unit |

|-----------------------------------------------|-----|-----|------|

| VIN                                           | 6   | 20  | V    |

| VDRV                                          | 4   | 10  | V    |

| PWM, PWMB                                     | 0   | 5   | V    |

| Operating Junction Temperature T <sub>J</sub> | -40 | 125 | °C   |

## **10. Thermal Information**

| Symbol           | Parameter                                   | INS1001DE | Unit |

|------------------|---------------------------------------------|-----------|------|

| R <sub>0JA</sub> | Thermal Resistance, Junction to Ambient     | 70.8      | °C/W |

| Rejc(top)        | Thermal Resistance, Junction to Case Top    | 67.2      | °C/W |

| Rejc(bot)        | Thermal Resistance, Junction to Case Bottom | 10.3      | °C/W |

Page 4

### **POWER THE FUTURE**

www.innoscience.com

DS Rev1.0 2024/01/30

### **11. Electrical Characteristics**

$T_A = 25^{\circ}C$ , VIN = 12V,  $C_{DRV} = 1$ uF,  $C_{LDO5} = 1$ uF, OUTH = OUTL, unless otherwise noted.

| Parameter                                 | Symbol               | Min  | Тур  | Мах  | Unit | Test Condition                         |

|-------------------------------------------|----------------------|------|------|------|------|----------------------------------------|

| Supply Input                              | 1                    |      | 1    |      |      |                                        |

| VIN UVLO threshold                        | V <sub>IN_UVLO</sub> |      | 5.5  | 5.8  | V    | VIN rising                             |

| VIN UVLO hysteresis                       | V <sub>IN_HYS</sub>  |      | 0.35 |      | V    |                                        |

| VIN quiescent current                     | Ivin_q               |      | 200  |      | uA   | PMW = PWMB = 0V                        |

| PWM/PWMB Input                            |                      |      |      |      |      |                                        |

| Input high threshold                      | VIH                  |      | 2.6  | 3.2  | V    |                                        |

| Input low threshold                       | VIL                  | 0.8  | 1.4  |      | V    |                                        |

| PWM pulldown resistance                   | Rpwm                 |      | 200  |      | kΩ   | To GND pin                             |

| PWMB pullup resistance                    | Rpwmb                |      | 200  |      | kΩ   | To LDO5 pin                            |

| VDRV Regulation                           |                      |      |      |      |      |                                        |

| ADJ regulation voltage                    | Vadj                 | 0.97 | 1    | 1.03 | V    |                                        |

| ADJ UVLO threshold                        | Vadj_uvlo            | 0.8  | 0.85 | 0.9  | V    | ADJ rising                             |

| ADJ UVLO hysteresis                       | VADJ_HYS             |      | 0.05 |      | V    |                                        |

| VDRV current limit                        | I <sub>DRV</sub>     | 35   | 55   | 70   | mA   |                                        |

| VDRV dropout voltage                      | Vdrv_do              |      | 140  | 250  | mV   | VIN = 6V, ADJ = 0V, I <sub>DRV</sub> = |

|                                           |                      |      |      |      |      | 20mA                                   |

| VDRV OVP threshold                        | V <sub>DRV_OVP</sub> | 11   | 11.5 | 12   | V    | VDRV rising                            |

| VDRV OVP hysteresis                       |                      |      | 0.5  |      | V    |                                        |

| LDO5 Regulation                           |                      |      |      |      |      |                                        |

| LDO5 regulation voltage                   | VLD05                | 4.85 | 5    | 5.15 | V    |                                        |

| LDO5 UVLO threshold                       | VLDO5_UVLO           | 3.8  | 4    | 4.2  | V    | LDO5 rising                            |

| LDO5 UVLO hysteresis                      | VLDO5_HYS            |      | 0.3  |      | V    |                                        |

| LDO5 current limit                        | ILDO5                |      | 38   |      | mA   |                                        |

| LDO5 dropout voltage                      | VLDO5_DO             |      | 130  | 250  | mV   | VIN = 5V, I <sub>LDO5</sub> = 10mA     |

| Gate Driver                               |                      |      |      |      |      |                                        |

| OUTH pull-up resistance                   | Routh                |      | 1.3  |      | Ω    | VDRV = 6V, IOUTH = -100mA              |

| OUTL pull-down resistance                 | ROUTL                |      | 0.5  |      | Ω    | Iou⊤∟ = 100mA                          |

| OUTH peak source current (1)              | Іоитн                |      | 2    |      | А    |                                        |

| OUTL peak sink current <sup>(1)</sup>     | Ioutl                |      | 5.5  |      | А    |                                        |

| Thermal Protection                        |                      |      |      |      |      |                                        |

| Thermal shutdown threshold <sup>(1)</sup> | T <sub>SD</sub>      |      | 160  |      | °C   |                                        |

| Thermal hysteresis <sup>(1)</sup>         | T <sub>HYS</sub>     |      | 20   |      | °C   |                                        |

Page 5

### POWER THE FUTURE

www.innoscience.com

DS Rev1.0 2024/01/30

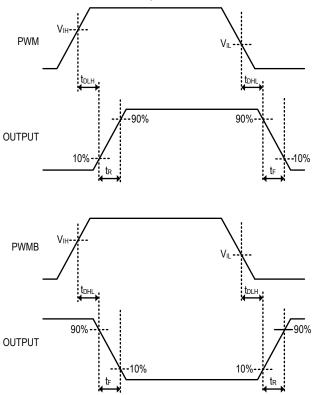

## **12. Switching Characteristics**

$T_A = 25^{\circ}C$ , VIN = 12V, VDRV = 6V,  $C_{DRV} = 1$ uF,  $C_{LDO5} = 1$ uF, OUTH = OUTL, unless otherwise noted.

| Parameter                                 | Symbol           | Min | Тур | Мах | Unit | Test Condition      |

|-------------------------------------------|------------------|-----|-----|-----|------|---------------------|

| Minimum input high pulse                  | t <sub>HPW</sub> |     | 15  |     | ns   |                     |

| width <sup>(1)</sup>                      |                  |     |     |     |      |                     |

| Minimum input low pulse width             | t <sub>LPW</sub> |     | 15  |     | ns   |                     |

| Output rise time <sup>(1)</sup>           | t <sub>R</sub>   |     | 10  |     | ns   | Fig. 16, Cout = 1nF |

| Output fall time <sup>(1)</sup>           | t⊧               |     | 3   |     | ns   | Fig. 16, Cout = 1nF |

| Turn-on propagation delay <sup>(1)</sup>  | t <sub>DLH</sub> |     | 35  | 50  | ns   | Fig. 16             |

| Turn-off propagation delay <sup>(1)</sup> | t <sub>DHL</sub> |     | 35  | 50  | ns   | Fig. 16             |

(1) Not 100% tested and guaranteed by design.

Page 6

#### **POWER THE FUTURE**

www.innoscience.com

DS Rev1.0 2024/01/30

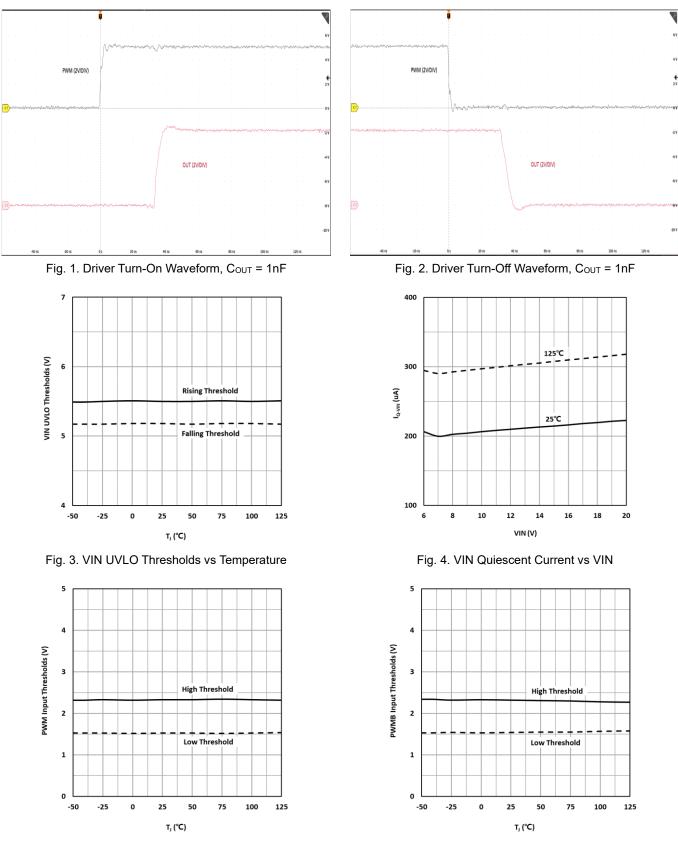

## **13. Typical Characteristics**

Fig. 5. PWM Input Thresholds vs Temperature

Fig. 6. PWMB Input Thresholds vs Temperature

Page 7

### **POWER THE FUTURE**

www.innoscience.com

DS Rev1.0 2024/01/30

**Innoscience**

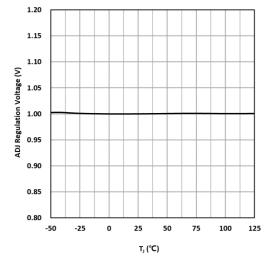

Fig. 7. ADJ Regulation Voltage vs Temperature

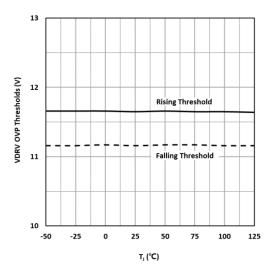

Fig. 9. VDRV OVP Thresholds vs Temperature

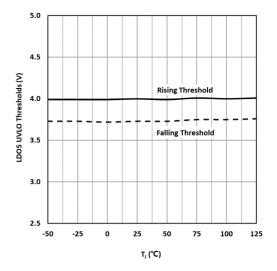

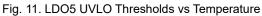

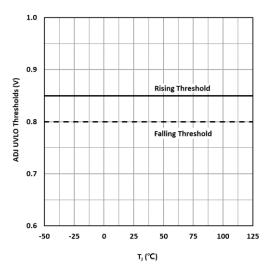

Fig. 8. ADJ UVLO Thresholds vs Temperature

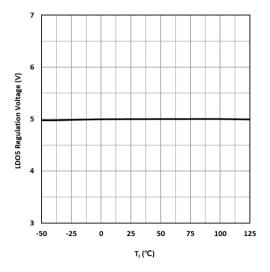

Fig. 10. LDO5 Regulation Voltage vs Temperature

Page 8

#### **POWER THE FUTURE**

www.innoscience.com

DS Rev1.0 2024/01/30

**Innoscience**

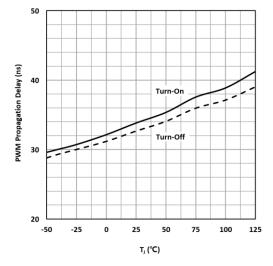

Fig. 13. PWM Propagation Delay vs Temperature

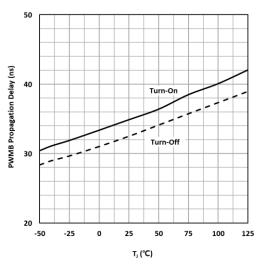

Fig. 14. PWMB Propagation Delay vs Temperature

Page 9

#### **POWER THE FUTURE**

www.innoscience.com

DS Rev1.0 2024/01/30

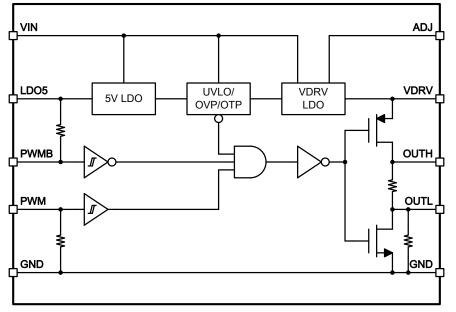

### 14. Block Diagram

Fig. 15. Functional Block Diagram

## **15. Function Description**

The INS1001 is a full-featured, single-channel gate driver that is fully optimized to drive a single GaN FET or multiple paralleling GaN FETs in either low-side, high-side, or secondary-side SR applications. The INS1001 solves many of the conventional challenges faced in the applications implementing GaN FETs. It features two separate non-inverting (PWM) and inverting (PWMB) inputs, working with controller, opto-coupler, and digital isolator flexibly. The split output gate driver allows independent adjustment of turn-on and turn-off speeds. The driver voltage of the INS1001 can be precisely adjusted with external resistor divider, tailoring for different gate voltage requirements of GaN FETs. Integrated 5V LDO can supply digital isolator or other circuitry in high-side applications. The strong driving capability and fast propagation delay, along with input noise deglitching and built-in UVLO, OVP, OTP protection features, make the INS1001 extremely suitable for high power, high frequency, and robust power GaN applications. Its operation is best understood by referring to the Block Diagram in Fig. 15.

### **PWM Input and Output**

The INS1001 has two separate non-inverting (PWM) and inverting (PWMB) CMOS logic input pins to drive singlechannel GaN FETs, enabling it to work with controller, opto-coupler, and digital isolator flexibly. The PWM and PWMB input states are summarized in Table 1. When the PWMB pin is low, the driver output (OUTH, OUTL) is synchronized with the PWM input logic. When the PWM pin is high, the driver output is synchronized with the PWMB pin logic.

| PWM | PWMB | OUTH    | OUTL      |

|-----|------|---------|-----------|

| L   | L    | Open    | Pull-Down |

| L   | Н    | Open    | Pull-Down |

| Н   | L    | Pull-Up | Open      |

| Н   | Н    | Open    | Pull-Down |

Table 1. PWM and PWMB input states

Page 10

### **POWER THE FUTURE**

www.innoscience.com

DS Rev1.0 2024/01/30

# Innoscience

The logic input signals are independent of VIN. For example, the logic inputs are provided from a 3.3V/5V CMOS logic, while the IC is powered from 12V Supply. The CMOS logic inputs have the upper and the lower thresholds of 2.8V (Max) and 1.2V (Min) respectively with a 15ns (typical) input deglitching time to avoid any fault triggering condition such as double pulsing during transition. The PWM logic input pin has an internal 200k $\Omega$  pulldown resistor to the GND pin, and the PWMB logic input pin has an internal 200k $\Omega$  pull-up resistor to the LDO5 pin.

#### **Split Gate Driving Outputs**

It is often practiced reducing gate drive pull-up strengths in driving GaN FET switches by adding an external gate resistor, to prevent the large dv/dt induced switching spikes that deteriorates reliability and EMI. Then again, strong pull-down gate drive is always required because the fast slew rate of drain of GaN FET (SW) node may pull up the gate of the GaN FET and falsely turn it on. A traditional single gate drive can only have a single gate resistor that cannot optimize both requirements at the same time. In the INS1001, a split gate drive is provided, which allows the use of a large pull-up resistor and low pull-down resistor to achieve optimized efficiency, reliability, and EMI performance. Figure 16 illustrates the switching timing waveforms of the driver outputs.

Figure 16. Circuit diagram of V<sub>DRV</sub> regulation loop

### LDO5 Regulator

An internal P-channel low dropout regulator produces 5V at the LDO5 pin from the V<sub>IN</sub> supply pin. The LDO5 powers the internal circuitry in the INS1001 and can also supply digital isolator in high-side applications. The LDO5 regulator can supply a peak current of 38mA (typical) and must be bypassed to ground with a minimum of 1µF ceramic capacitor.

#### VIN Undervoltage Lockout (UVLO)

The INS1001 features  $V_{IN}$  undervoltage lockout (UVLO) protection. When  $V_{IN}$  is below its UVLO threshold, 5.5V (typical), the INS1001 enters  $V_{IN}$  UVLO mode and turns off the driver.

#### Page 11

### **POWER THE FUTURE**

www.innoscience.com

DS Rev1.0 2024/01/30

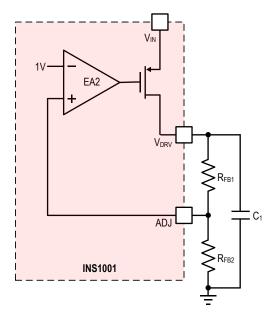

#### **VDRV Regulator**

Figure 17. Circuit diagram of V<sub>DRV</sub> regulation loop

The INS1001 has an integrated LDO for adjustable gate driver output voltage ( $V_{DRV}$ ), which can be programmed through control of two external resistors. Figure 17 demonstrates the  $V_{DRV}$  closed loop regulation through the ADJ pin and two external resistors. The ADJ pin is the negative feedback input pin that is regulated at 1V (typical) internal reference voltage, and thus the  $V_{DRV}$  is regulated to:

$$V_{DRV} = 1V \times \frac{R_{FB1} + R_{FB2}}{R_{FB2}}$$

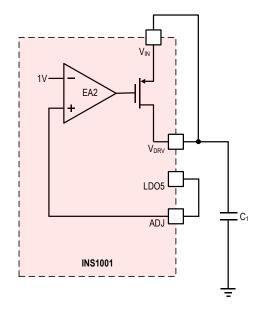

The  $V_{DRV}$  regulator can supply a peak current of 55mA (typical) and must be bypassed to ground with a minimum of 1µF ceramic capacitor (C<sub>1</sub>). When  $V_{DRV}$  passes its OVLO threshold, 11.5V (typical), the INS1001 enters to the  $V_{DRV}$  clamp mode and disables  $V_{DRV}$  regulator. When supplying  $V_{DRV}$  directly from  $V_{IN}$ , the recommended pin configuration is shown in Figure 18.

Figure 18. Configuration of V<sub>DRV</sub> supplied directly from V<sub>IN</sub>

Page 12

#### **POWER THE FUTURE**

www.innoscience.com

DS Rev1.0 2024/01/30

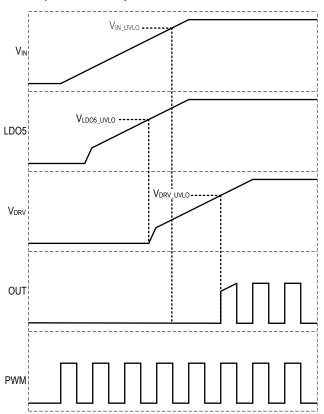

#### **Startup Power Sequence**

Figure 19 shows the start-up power sequence for the INS1001. Once the V<sub>IN</sub> is supplied and rises enough to wake up startup circuitry, the INS1001 generates bandgap reference and powers up the internal LDO5 LDO. The LDO5 LDO supplies the internal V<sub>DRV</sub> control circuitry and now the INS1001 enters LDO5 undervoltage lockout (UVLO) mode. When the LDO5 pin is charged above its rising UVLO threshold (4V typical), the V<sub>IN</sub> pin passes its rising enable threshold (5.5V typical), and the junction temperature is less than its thermal shutdown (160°C typical), the INS1001 powers up the V<sub>DRV</sub> LDO and now the INS1001 enters V<sub>DRV</sub> UVLO mode. From the time of entering V<sub>DRV</sub> UVLO mode to the time of V<sub>DRV</sub> passing its rising UVLO threshold, (85% of ADJ pin voltage typical), the INS1001 is going through a power-on-reset (POR), waking up the entire internal driver control circuitry and settling to the right initial conditions. After the POR, the INS1001 starts passing the PWM inputs to its output.

Figure 19. Waveforms of startup power sequence

Page 13

#### **POWER THE FUTURE**

www.innoscience.com

DS Rev1.0 2024/01/30

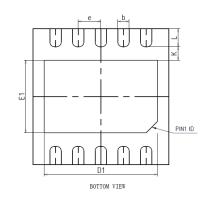

## 16. Package Information

## DFN3X3-10L Package:

| SYMBOL  | MILLIMETER |      |      |  |  |

|---------|------------|------|------|--|--|

| STRIBUL | MIN        | NOM  | MAX  |  |  |

| А       | 0.70       | 075  | 0.80 |  |  |

| A1      | 0.00       | 0.02 | 0.05 |  |  |

| A2      | 0.203REF   |      |      |  |  |

| b       | 0.18       | 0.25 | 0.30 |  |  |

| D       | 2.90       | 3.00 | 3.10 |  |  |

| D1      | 2.20       | 2.50 | 2.70 |  |  |

| e       | 0.50BSC    |      |      |  |  |

| E       | 2.90       | 3.00 | 3.10 |  |  |

| E1      | 1.40       | 1.60 | 1.80 |  |  |

| L       | 0.30       | 0.40 | 0.50 |  |  |

| К       | 0.30REF    |      |      |  |  |

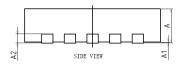

| ROW  | Description      | Example  |

|------|------------------|----------|

| Row1 | Product Code     | XXXXXXXX |

| Row2 | Assembly Lot No. | XXXXXXXX |

| Row3 | Date Code        | YYWW     |

Page 14

#### **POWER THE FUTURE**

www.innoscience.com

DS Rev1.0 2024/01/30

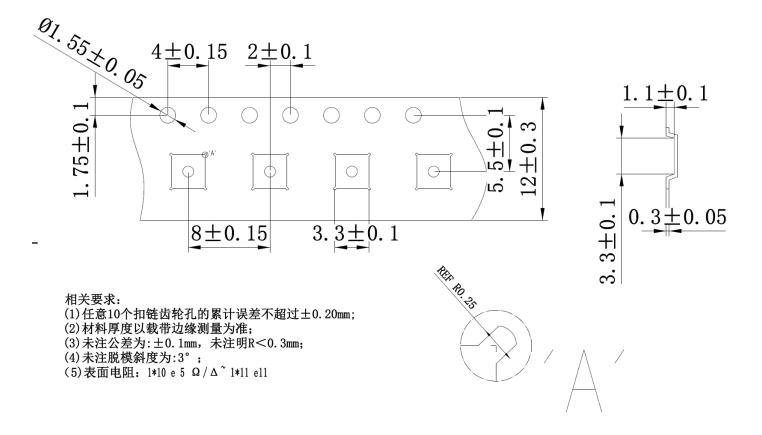

### 17. Tape and Reel Information

Page 15

#### **POWER THE FUTURE**

www.innoscience.com

DS Rev1.0 2024/01/30

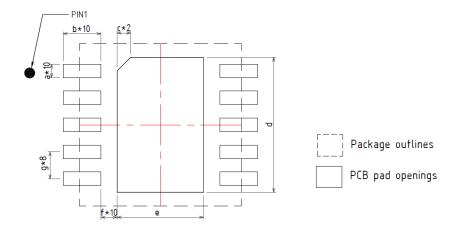

### **18. Recommended Land Pattern**

| SYMBOL                                                                        | DIMENSION | SYMBOL | DIMENSION |  |  |  |  |

|-------------------------------------------------------------------------------|-----------|--------|-----------|--|--|--|--|

|                                                                               |           |        |           |  |  |  |  |

| а                                                                             | 0.250     | е      | 1.600     |  |  |  |  |

| Ь                                                                             | 0.700     | f      | 0.300     |  |  |  |  |

| С                                                                             | 0.250     | g      | 0.500     |  |  |  |  |

| d                                                                             | 2.500     |        |           |  |  |  |  |

| Notes:<br>(1)All dimension are in millimeters.<br>(2)Drawing is not to scale. |           |        |           |  |  |  |  |

## **19. Order Information**

| Ordering<br>Code | Package    | Product<br>Code | MSL  | Packing<br>(Tape & Reel) |

|------------------|------------|-----------------|------|--------------------------|

| INS1001DE        | DFN3x3-10L | 1001DE          | MSL3 | 13" 2500PCS/reel         |

Page 16

#### **POWER THE FUTURE**

www.innoscience.com

DS Rev1.0 2024/01/30

### **Important Notice**

The information provided in this document is intended as a guide only and shall not in any event be regarded as a guarantee of conditions, characteristics, or performance. Innoscience does not assume any liability arising out of the application or use of any product described herein, including but not limited to any personal injury, death, or property or environmental damage. No licenses, patent rights, or any other intellectual property rights is granted or conveyed. Innoscience reserves the right to modify without notice. All rights reserved.

Page 17

#### **POWER THE FUTURE**

www.innoscience.com

DS Rev1.0 2024/01/30

单击下面可查看定价,库存,交付和生命周期等信息

>>Innoscience(英诺赛科)