# **Application Note: SA21345D**

40V 150mA LDO Regulator

Advanced Design Specification

## **General Description**

SA21345D is a 150mA high current capacity linear regulator. It fixed the output voltage at 5V, which features ultra-low ground current and low drop out voltage. The device with fully protection includes over current limit, output short protection and over temperature protection.

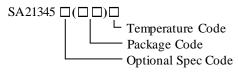

### **Ordering Information**

| Ordering Number | Package type | Note |

|-----------------|--------------|------|

| SA21345DAAA     | SOT23-5      |      |

### **Features**

- Wide Input Voltage Range: 4V to 36V

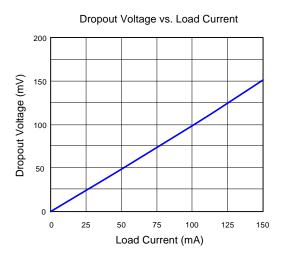

- Low Dropout Voltage (150mV @ 150mA)

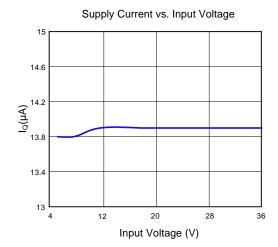

- Ultra-low Quiescent Current

- Stability with Tantalum or Ceramic Capacitors

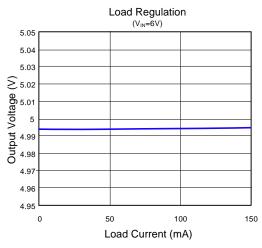

- Excellent Load and Line Regulation

- 150mA Maximum Load Current

- Over Current Protection

- Thermal Shutdown

- Compact SOT23-5 Package

- Automotive AEC- Q100 Grade 1 Certified

## **Applications**

- Note Book

- Cell Phone

- Automotive LED Lighting ECU

- Automotive Body Modules

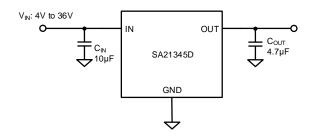

## **Typical Applications**

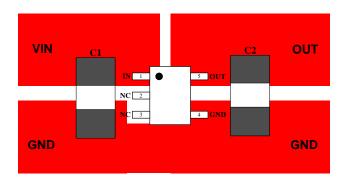

Figure 1 Schematic Diagram

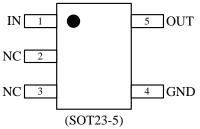

### **Pinout (Top view)**

Top mark:  $\mathbf{H3}xyz$  (Device code: H3, x=year code, y=week code, z=lot number code)

| Pin Name | Pin number | ber Pin Description                                           |  |

|----------|------------|---------------------------------------------------------------|--|

| IN       | 1          | Input pin, decoupled with at least 1µF MLCC capacitor to GND. |  |

| GND      | 4          | Ground pin                                                    |  |

| OUT      | 5          | Output pin, decoupled with a 4.7µF MLCC capacitor to GND.     |  |

| NC       | 2,3        | No Connection                                                 |  |

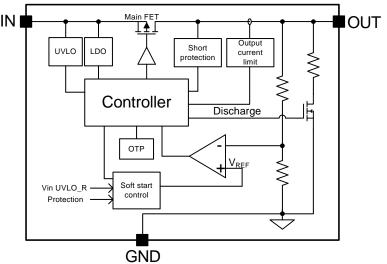

# **Block Diagram**

# Absolute Maximum Ratings (Note 1)

| IN to GND                                        |            |

|--------------------------------------------------|------------|

| OUT to GND                                       | 0.3V to 8V |

| Power Dissipation, PD @ TA = 25°C                | 0.47W      |

| Package Thermal Resistance (Note 2)              |            |

| heta JA                                          | 210°C/W    |

| heta 1C                                          | 38.4°C/W   |

| Junction Temperature                             |            |

| Lead Temperature (Soldering, 10 sec.)            | 260°C      |

| Storage Temperature Range                        |            |

| ESD Susceptibility                               |            |

| HBM (Human Body Mode)                            | 2kV        |

| CDM (Charged Device Mode)                        | 500V       |

| <b>Recommended Operating Conditions</b> (Note 3) |            |

| Supply Input Voltage                             | 4V to 36V  |

|                                                  |            |

### **Electrical Characteristics**

$V_{IN} = 12V$ ,  $T_J = -40^{\circ}C \sim 125^{\circ}C$ , unless otherwise specified, the values are guaranteed by test design or statistical correlation

| Parameter                            | Symbol                 | Test Conditions                                                                                                                               | Min  | Тур  | Max  | Unit |

|--------------------------------------|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| Input Voltage                        | V <sub>IN</sub>        |                                                                                                                                               | 4    |      | 36   | V    |

| Input Voltage UVLO<br>Threshold      | V <sub>ULVO</sub>      | V <sub>IN</sub> rising                                                                                                                        | 2.9  | 3.3  | 4    | V    |

| UVLO Hysteresis                      | V <sub>UVLO_HYS</sub>  |                                                                                                                                               |      | 200  |      | mV   |

| Output Voltage                       | $V_{OUT}$              | $T_{J} = -40^{\circ}C \sim 125^{\circ}C$                                                                                                      | 4.9  | 5    | 5.1  | V    |

| Output Voltage                       |                        | $T_J = 25$ °C                                                                                                                                 | 4.95 | 5    | 5.05 | V    |

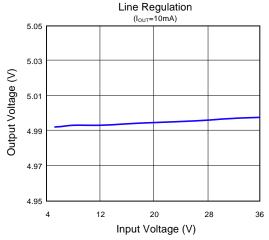

| Line Regulation                      | $\Delta V_{LNR}$       | $I_{OUT} = 10 \text{mA}, 5.5 \text{V} \le V_{IN} \le 36 \text{V}$                                                                             |      | 1    | 1.5  | mV/V |

| Load Regulation                      | $\Delta V_{LDR}$       | $V_{IN}=6V, 10mA \le I_{OUT} \le 0.15V$                                                                                                       |      | 0.25 | 0.5  | %    |

| Daniel William                       | $\Delta V_{DROP}$      | I <sub>OUT</sub> =10mA                                                                                                                        |      | 10   | 20   | mV   |

| Dropout Voltage                      |                        | I <sub>OUT</sub> =150mA                                                                                                                       |      | 150  | 300  | mV   |

| Quiescent Current I <sub>Q</sub>     |                        | $I_{OUT}$ =0mA<br>$V_{IN}$ =( $V_{OUT}$ +1 $V$ ) ~ 36 $V$                                                                                     |      | 15   | 22   | μΑ   |

| Current Limit                        | $I_{LMT}$              | Force $V_{OUT} = 4.5V$                                                                                                                        | 600  |      |      | mA   |

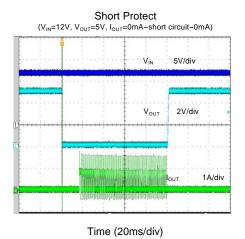

| Output Short<br>Protection Threshold | V <sub>SHORT</sub>     | Force V <sub>OUT</sub> from 5V to 0V                                                                                                          | 0.4  | 0.8  | 1.5  | V    |

| Output Short Off Time                | t <sub>SHORT_OFF</sub> |                                                                                                                                               |      | 16   |      | ms   |

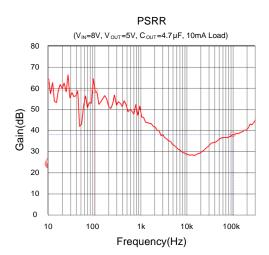

| Power Supply                         | PSRR                   | Frequency = 100Hz,<br>C <sub>OUT</sub> =4.7µF, I <sub>OUT</sub> =10mA T <sub>A</sub> =25°C                                                    |      | 60   |      | dB   |

| Rejection Ratio                      |                        | Frequency = $100\text{kHz}$ ,<br>$C_{\text{OUT}}$ = $4.7\mu\text{F}$ , $I_{\text{OUT}}$ = $10\text{mA}$ $T_{\text{A}}$ = $25^{\circ}\text{C}$ |      | 35   |      | dB   |

| Output Discharge<br>Resistor         | R <sub>DIS</sub>       | V <sub>IN</sub> =3V, V <sub>OUT</sub> =2V                                                                                                     |      | 500  |      | Ω    |

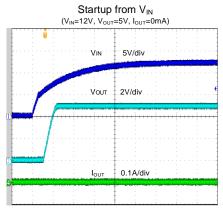

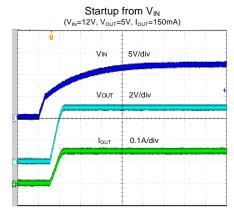

| Soft-start Time                      | $t_{SS}$               |                                                                                                                                               |      | 1    |      | ms   |

| Thermal Shutdown Temperature         | $T_{SD}$               |                                                                                                                                               |      | 150  |      | °C   |

| Thermal Shutdown<br>Hysteresis       | T <sub>HYS</sub>       |                                                                                                                                               |      | 20   |      | °C   |

**Note 1**: Stresses beyond the "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only. Functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

Note 2:  $\theta$  JA is measured in the natural convection at  $T_A = 25^{\circ}$ C on a low effective single layer thermal conductivity test board of JEDEC 51-3 thermal measurement standard.

**Note 3:** The device is not guaranteed to function outside its operating conditions.

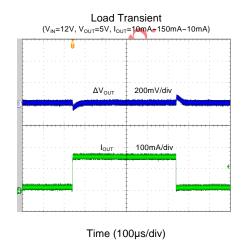

# **Typical Performance Characteristics**

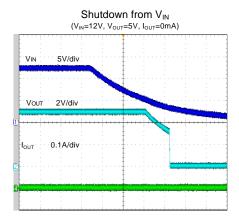

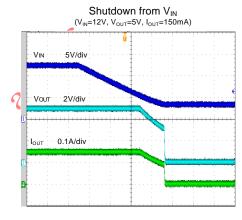

Time (2ms/div)

Time (400ms/div)

Time (10ms/div)

## **Operation**

SA21345D is a 150mA high current capacity linear regulator. It fixed the output voltage at 5V, which features ultra-low ground current and low drop out voltage. The device with fully protection includes over current limit, output short protection and over temperature protection.

## **Applications Information**

#### **Over Temperature Protection (OTP)**

SA21345D includes over-temperature protection (OTP) circuitry to prevent overheating due to excessive power dissipation. This will turn off the device when the junction temperature exceeds 150°C. Once the junction temperature cools down by approximately 20°C the IC will resume normal operation

#### **Output Short Circuit Protect**

If  $V_{OUT}$  drop below than 0.8V, the short circuit protection mode will be initiated, and the device will be shut down for approximately 16ms. The device will then restart with a complete soft-start cycle. If the short circuit condition remains another 'hiccup' cycle of shutdown and restart will continue indefinitely unless the OTP threshold is reached.

#### Input Capacitor C<sub>IN</sub>

To minimize the potential noise problem and improve power-supply rejection(PSRR) and transient response, place a typical X5R or better grade ceramic capacitor really close to the IN and GND pins. Care should be taken to minimize the loop area formed by C<sub>IN</sub>, and IN/GND pins. In this case, a 4.7uF low ESR ceramic capacitor is recommended.

#### **Output Capacitor Cout**

For stable operation over the full temperature range, a  $4.7\mu F$  low-ESR ceramic capacitor is recommended. Use larger output-capacitor values such as  $22\mu F$  to reduce noise, improve load-transient response and PSRR. Some ceramic dielectrics exhibit large capacitance and ESR variations with temperature.

#### **PCB Layout Guide**

For best performance of the SA21345D, the following guidelines must be strictly followed:

- 1. Keep all power trace as short and wide as possible. And it is desirable to use 2-layer or 4-layer board for thermal performance and better capability of current flow.

- 2. Place input/output capacitor close to the IC for better transient performance.

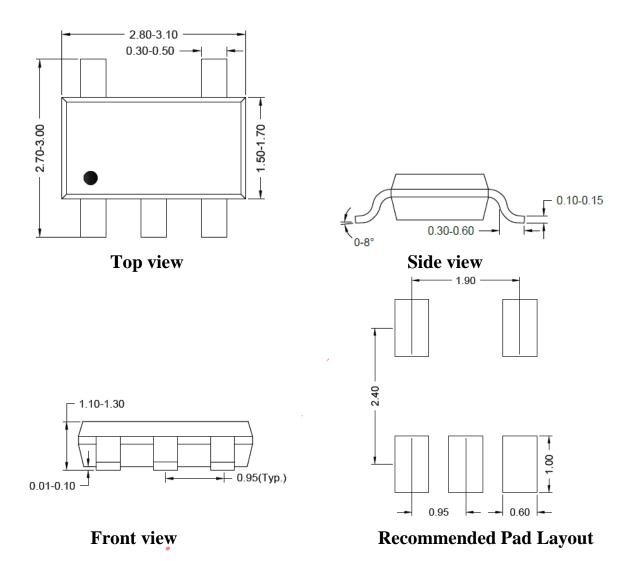

# **SOT23-5 Package Outline & PCB layout**

Notes: All dimension in millimeter and exclude mold flash & metal burr.

# **Taping & Reel Specification**

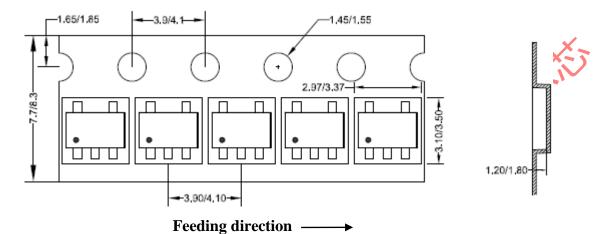

### 1. Taping orientation

### **SOT23-5**

## 2. Carrier Tape & Reel specification for packages

| Package<br>type | Tape width (mm) | Pocket pitch(mm) | Reel size<br>(Inch) | Trailer<br>length(mm) | Leader length (mm) | Qty per<br>reel |

|-----------------|-----------------|------------------|---------------------|-----------------------|--------------------|-----------------|

| SOT23-5         | 8               | 4                | 7''                 | 280                   | 160                | 3000            |

### 3. Others: NA

## 单击下面可查看定价,库存,交付和生命周期等信息

>>SILERGY(矽力杰)