# **ESP32-S3 Series**

Datasheet Version 1.9

Xtensa<sup>®</sup> 32-bit LX7 dual-core microprocessor 2.4 GHz Wi-Fi (IEEE 802.11b/g/n) and Bluetooth<sup>®</sup> 5 (LE) Optional 1.8 V or 3.3 V flash and PSRAM in the chip's package 45 GPIOs QFN56 (7×7 mm) Package

### Including:

ESP32-S3 ESP32-S3FN8 ESP32-S3R2 ESP32-S3R8 ESP32-S3R8V ESP32-S3R16V ESP32-S3FH4R2

# **Product Overview**

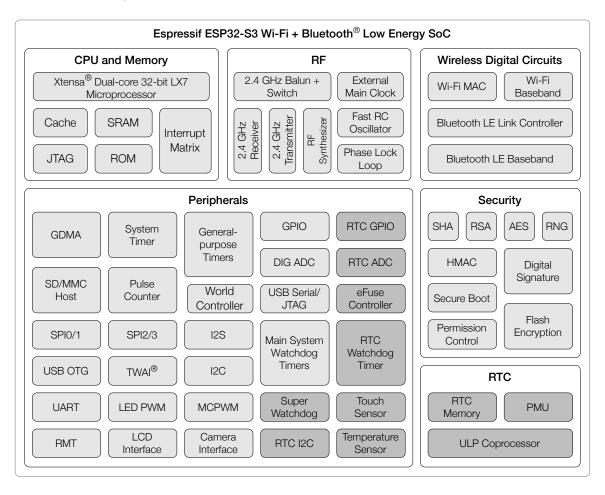

ESP32-S3 is a low-power MCU-based system on a chip (SoC) with integrated 2.4 GHz Wi-Fi and Bluetooth<sup>®</sup> Low Energy (Bluetooth LE). It consists of high-performance dual-core microprocessor (Xtensa<sup>®</sup> 32-bit LX7), a ULP coprocessor, a Wi-Fi baseband, a Bluetooth LE baseband, RF module, and numerous peripherals.

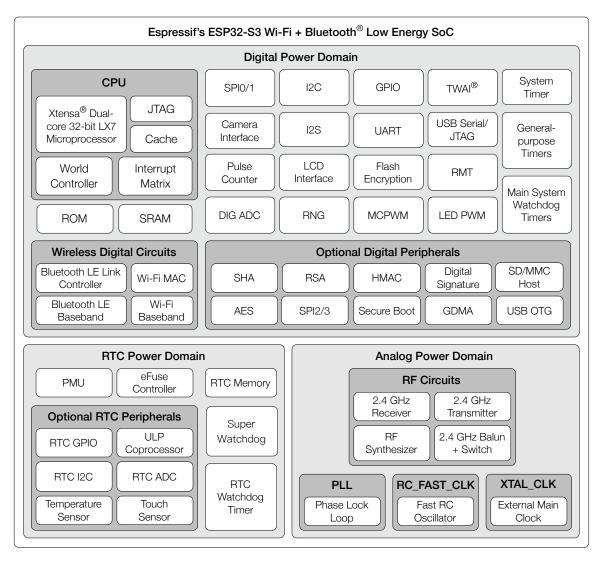

The functional block diagram of the SoC is shown below.

Power consumption

) Normal

Low power consumption components capable of working in Deep-sleep mode

ESP32-S3 Functional Block Diagram

For more information on power consumption, see Section 4.1.3.5 Power Management Unit (PMU).

### Features

#### Wi-Fi

- IEEE 802.11b/g/n-compliant

- Supports 20 MHz and 40 MHz bandwidth in 2.4 GHz band

- 1T1R mode with data rate up to 150 Mbps

- Wi-Fi Multimedia (WMM)

- TX/RX A-MPDU, TX/RX A-MSDU

- Immediate Block ACK

- Fragmentation and defragmentation

- Automatic Beacon monitoring (hardware TSF)

- Four virtual Wi-Fi interfaces

- Simultaneous support for Infrastructure BSS in Station, SoftAP, or Station + SoftAP modes Note that when ESP32-S3 scans in Station mode, the SoftAP channel will change along with the Station channel

- Antenna diversity

- 802.11mc FTM

#### Bluetooth

- Bluetooth LE: Bluetooth 5, Bluetooth mesh

- High power mode (20 dBm)

- Speed: 125 Kbps, 500 Kbps, 1 Mbps, 2 Mbps

- Advertising extensions

- Multiple advertisement sets

- Channel selection algorithm #2

- Internal co-existence mechanism between Wi-Fi and Bluetooth to share the same antenna

#### **CPU and Memory**

- Xtensa<sup>®</sup> dual-core 32-bit LX7 microprocessor

- Clock speed: up to 240 MHz

- CoreMark<sup>®</sup> score:

- One core at 240 MHz: 613.86 CoreMark; 2.56 CoreMark/MHz

- Two cores at 240 MHz: 1181.60 CoreMark; 4.92 CoreMark/MHz

- Five-stage pipeline

- 128-bit data bus and dedicated SIMD instructions

Espressif Systems

- Single precision floating point unit (FPU)

- L1 cache

- ROM: 384 KB

- SRAM: 512 KB

- SRAM in RTC: 16 KB

- Supported SPI protocols: SPI, Dual SPI, Quad SPI, Octal SPI, QPI and OPI interfaces that allow connection to flash, external RAM, and other SPI devices

- Flash controller with cache is supported

- Flash in-Circuit Programming (ICP) is supported

#### **Advanced Peripheral Interfaces**

- 45 programmable GPIOs

- 4 strapping GPIOs

- 6 or 7 GPIOs needed for in-package flash or PSRAM

- \* ESP32-S3FN8、ESP32-S3R2、ESP32-S3R8、ESP32-S3R8V、ESP32-S3R16V: 6 GPIOs needed

- \* ESP32-S3FH4R2: 7 GPIOs needed

- Digital interfaces:

- Two SPI ports for communication with flash and RAM

- Two general-purpose SPI ports

- LCD interface (8-bit ~ 16-bit parallel RGB, I8080 and MOTO6800), supporting conversion between RGB565, YUV422, YUV420 and YUV411

- DVP 8-bit ~ 16-bit camera interface

- Three UARTs

- Two I2Cs

- Two I2Ss

- RMT (TX/RX)

- Pulse counter

- LED PWM controller, up to 8 channels

- Full-speed USB OTG

- USB Serial/JTAG controller

- Two Motor Control PWMs (MCPWM)

- SD/MMC host controller with 2 slots

- General DMA controller (GDMA), with 5 transmit channels and 5 receive channels

- TWAI<sup>®</sup> controller, compatible with ISO 11898-1 (CAN Specification 2.0)

- On-chip debug functionality via JTAG

- Analog interfaces:

- Two 12-bit SAR ADCs, up to 20 channels

- Temperature sensor

- 14 touch sensing IOs

- Timers:

- Four 54-bit general-purpose timers

- 52-bit system timer

- Three watchdog timers

#### Low Power Management

- Fine-resolution power control through a selection of clock frequency, duty cycle, Wi-Fi operating modes, and individual power control of internal components

- Four power modes designed for typical scenarios: Active, Modem-sleep, Light-sleep, Deep-sleep

- Power consumption in Deep-sleep mode is as low as 7  $\mu$ A

- Ultra-Low-Power (ULP) coprocessors:

- ULP-RISC-V coprocessor

- ULP-FSM coprocessor

- RTC memory remains powered on in Deep-sleep mode

#### Security

- Secure boot

- Flash encryption

- 4-Kbit OTP, up to 1792 bits for users

- Cryptographic hardware acceleration:

- AES-128/256 (FIPS PUB 197)

- SHA (FIPS PUB 180-4)

- RSA

- Random Number Generator (RNG)

- HMAC

- Digital signature

### **Applications**

With low power consumption, ESP32-S3 is an ideal choice for IoT devices in the following areas:

- Smart Home

- Industrial Automation

- Health Care

- Consumer Electronics

- Smart Agriculture

- POS machines

- Service robot

- Audio Devices

- Generic Low-power IoT Sensor Hubs

- Generic Low-power IoT Data Loggers

- Cameras for Video Streaming

- USB Devices

- Speech Recognition

- Image Recognition

- Wi-Fi + Bluetooth Networking Card

- Touch and Proximity Sensing

#### Note:

Check the link or the QR code to make sure that you use the latest version of this document: https://www.espressif.com/documentation/esp32-s3\_datasheet\_en.pdf

# Contents

| Pro                           | 2                                                                                                                                                                                                                                                        |                                        |

|-------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| Featu                         | 3                                                                                                                                                                                                                                                        |                                        |

| Appli                         | 5                                                                                                                                                                                                                                                        |                                        |

| <b>1</b>                      | ESP32-S3 Series Comparison                                                                                                                                                                                                                               | 13                                     |

| 1.1                           | Nomenclature                                                                                                                                                                                                                                             | 13                                     |

| 1.2                           | Comparison                                                                                                                                                                                                                                               | 13                                     |

| <b>2</b><br>2.1<br>2.2<br>2.3 | Pin Layout         Pin Overview         IO Pins         2.3.1       IO MUX Functions         2.3.2       RTC Functions         2.3.3       Analog Functions                                                                                              | 14<br>14<br>15<br>19<br>21<br>22       |

| 2.4<br>2.5<br>2.6             | <ul> <li>2.3.4 Restrictions for GPIOs and RTC_GPIOs</li> <li>Analog Pins</li> <li>Power Supply</li> <li>2.5.1 Power Pins</li> <li>2.5.2 Power Scheme</li> <li>2.5.3 Chip Power-up and Reset</li> <li>Pin Mapping Between Chip and Flash/PSRAM</li> </ul> | 24<br>25<br>26<br>26<br>26<br>27<br>28 |

| <b>3</b>                      | Boot Configurations                                                                                                                                                                                                                                      | 29                                     |

| 3.1                           | Chip Boot Mode Control                                                                                                                                                                                                                                   | 30                                     |

| 3.2                           | VDD_SPI Voltage Control                                                                                                                                                                                                                                  | 31                                     |

| 3.3                           | ROM Messages Printing Control                                                                                                                                                                                                                            | 31                                     |

| 3.4                           | JTAG Signal Source Control                                                                                                                                                                                                                               | 31                                     |

| <b>4</b><br>4.1               | Functional DescriptionSystem4.1.1Microprocessor and Master4.1.1CPU4.1.2Processor Instruction Extensions (PIE)4.1.3Ultra-Low-Power Coprocessor (ULP)4.1.4GDMA Controller (GDMA)                                                                           | 33<br>33<br>33<br>33<br>33<br>34<br>34 |

7

|     | 4.1.2  | Memory   | Organization                          | 35       |

|-----|--------|----------|---------------------------------------|----------|

|     |        | 4.1.2.1  | Internal Memory                       | 35       |

|     |        | 4.1.2.2  | External Flash and RAM                | 36       |

|     |        | 4.1.2.3  | Cache                                 | 36       |

|     |        | 4.1.2.4  | eFuse Controller                      | 37       |

|     | 4.1.3  | System ( | Components                            | 37       |

|     |        | 4.1.3.1  | IO MUX and GPIO Matrix                | 37       |

|     |        | 4.1.3.2  | Reset                                 | 38       |

|     |        | 4.1.3.3  | Clock                                 | 39       |

|     |        | 4.1.3.4  | Interrupt Matrix                      | 39       |

|     |        | 4.1.3.5  | Power Management Unit (PMU)           | 40       |

|     |        | 4.1.3.6  | System Timer                          | 42       |

|     |        | 4.1.3.7  | General Purpose Timers                | 42       |

|     |        | 4.1.3.8  | Watchdog Timers                       | 42       |

|     |        | 4.1.3.9  | XTAL32K Watchdog Timers               | 43       |

|     |        | 4.1.3.10 | Permission Control                    | 43       |

|     |        | 4.1.3.11 | World Controller                      | 44       |

|     |        | 4.1.3.12 | System Registers                      | 44       |

|     | 4.1.4  | Cryptogr | aphy and Security Component           | 45       |

|     |        | 4.1.4.1  | SHA Accelerator                       | 45       |

|     |        | 4.1.4.2  | AES Accelerator                       | 45       |

|     |        | 4.1.4.3  | RSA Accelerator                       | 46       |

|     |        | 4.1.4.4  | Secure Boot                           | 46       |

|     |        | 4.1.4.5  | HMAC Accelerator                      | 46       |

|     |        | 4.1.4.6  | Digital Signature                     | 47       |

|     |        | 4.1.4.7  | External Memory Encryption and Decry  | otion 47 |

|     |        | 4.1.4.8  | Clock Glitch Detection                | 47       |

|     |        | 4.1.4.9  | Random Number Generator               | 47       |

| 4.2 | Periph | erals    |                                       | 48       |

|     | 4.2.1  | Connect  | ivity Interface                       | 48       |

|     |        | 4.2.1.1  | UART Controller                       | 48       |

|     |        | 4.2.1.2  | I2C Interface                         | 49       |

|     |        | 4.2.1.3  | I2S Interface                         | 49       |

|     |        | 4.2.1.4  | LCD and Camera Controller             | 50       |

|     |        | 4.2.1.5  | Serial Peripheral Interface (SPI)     | 50       |

|     |        | 4.2.1.6  | Two-Wire Automotive Interface (TWAI®) | 53       |

|     |        | 4.2.1.7  | USB 2.0 OTG Full-Speed Interface      | 53       |

|     |        | 4.2.1.8  | USB Serial/JTAG Controller            | 55       |

|     |        | 4.2.1.9  | SD/MMC Host Controller                | 55       |

|     |        | 4.2.1.10 | LED PWM Controller                    | 56       |

|     |        | 4.2.1.11 | Motor Control PWM (MCPWM)             | 56       |

|     |        | 4.2.1.12 | Remote Control Peripheral (RMT)       | 57       |

|     |        | 4.2.1.13 | Pulse Count Controller (PCNT)         | 57       |

|     | 4.2.2  | Analog S | Signal Processing                     | 58       |

|     |        | 4.2.2.1  | SAR ADC                               | 58       |

|     |        | 4.2.2.2  | Temperature Sensor                    | 59       |

|     |        |          |                                       |          |

8 Submit Documentation Feedback

|     |         | 4.2.2.3             | Touch Sensor                            | 59       |

|-----|---------|---------------------|-----------------------------------------|----------|

| 4.3 |         | ss Commu            | inication                               | 60       |

|     | 4.3.1   | Radio               |                                         | 60       |

|     |         | 4.3.1.1             | 2.4 GHz Receiver                        | 60       |

|     |         |                     | 2.4 GHz Transmitter                     | 60       |

|     |         | 4.3.1.3             | Clock Generator                         | 60       |

|     | 4.3.2   | Wi-Fi               |                                         | 60       |

|     |         | 4.3.2.1             | Wi-Fi Radio and Baseband                | 61       |

|     |         | 4.3.2.2             | Wi-Fi MAC                               | 61       |

|     | 4.3.3   | 4.3.2.3<br>Bluetoot | Networking Features                     | 61<br>61 |

|     | 4.3.3   | 4.3.3.1             | Bluetooth LE PHY                        | 62       |

|     |         | 4.3.3.1             |                                         | 62       |

|     |         | 4.0.0.2             |                                         | 02       |

| 5   | Elec    | ctrical             | Characteristics                         | 63       |

| 5.1 | Absolu  | ite Maximu          | um Ratings                              | 63       |

| 5.2 |         |                     | Power Supply Characteristics            | 63       |

| 5.3 | VDD_S   | SPI Output          | Characteristics                         | 64       |

| 5.4 | DC Ch   | aracteristic        | cs (3.3 V, 25 °C)                       | 64       |

| 5.5 | ADC C   | haracterist         | tics                                    | 65       |

| 5.6 | Curren  | t Consum            | ption                                   | 65       |

|     | 5.6.1   | RF Curre            | nt Consumption in Active Mode           | 65       |

|     | 5.6.2   | Current (           | Consumption in Other Modes              | 66       |

| 5.7 | Reliabi | ility               |                                         | 67       |

| 6   | RF (    | Charac              | cteristics                              | 68       |

| 6.1 | Wi-Fi F | Radio               |                                         | 68       |

|     | 6.1.1   | Wi-Fi RF            | Transmitter (TX) Specifications         | 68       |

|     | 6.1.2   | Wi-Fi RF            | Receiver (RX) Specifications            | 70       |

| 6.2 | Blueto  | oth LE Rac          | dio                                     | 71       |

|     | 6.2.1   | Bluetoot            | h LE RF Transmitter (TX) Specifications | 71       |

|     | 6.2.2   | Bluetoot            | h LE RF Receiver (RX) Specifications    | 73       |

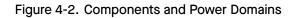

| 7   | Pac     | kaging              | g                                       | 76       |

| Ар  | oenc    | lix A –             | ESP32-S3 Consolidated Pin Overview      | 78       |

| Rel | ated    | Docu                | mentation and Resources                 | 79       |

| Rev | /isio   | n Histo             | ory                                     | 80       |

|     |         |                     | ·                                       |          |

# List of Tables

| 1-1  | ESP32-S3 Series Comparison                                   | 13 |

|------|--------------------------------------------------------------|----|

| 2-1  | Pin Overview                                                 | 15 |

| 2-2  | Power-Up Glitches on Pins                                    | 17 |

| 2-3  | Peripheral Signals Routed via IO MUX                         | 19 |

| 2-4  | IO MUX Pin Functions                                         | 20 |

| 2-5  | RTC Peripheral Signals Routed via RTC IO MUX                 | 22 |

| 2-6  | RTC Functions                                                | 22 |

| 2-7  | Analog Signals Routed to Analog Functions                    | 23 |

| 2-8  | Analog Functions                                             | 23 |

| 2-9  | Analog Pins                                                  | 25 |

| 2-10 | Power Pins                                                   | 26 |

| 2-11 | Voltage Regulators                                           | 26 |

| 2-12 | Description of Timing Parameters for Power-up and Reset      | 27 |

| 2-13 | Pin Mapping Between Chip and In-package Flash/ PSRAM         | 28 |

| 3-1  | Default Configuration of Strapping Pins                      | 29 |

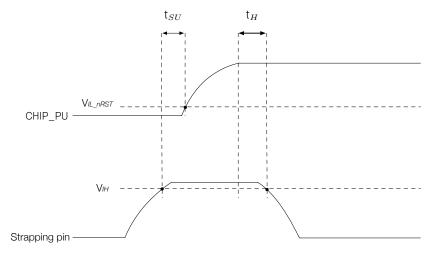

| 3-2  | Description of Timing Parameters for the Strapping Pins      | 30 |

| 3-3  | Chip Boot Mode Control                                       | 30 |

| 3-4  | VDD_SPI Voltage Control                                      | 31 |

| 3-5  | JTAG Signal Source Control                                   | 32 |

| 4-1  | Components and Power Domains                                 | 41 |

| 5-1  | Absolute Maximum Ratings                                     | 63 |

| 5-2  | Recommended Power Characteristics                            | 63 |

| 5-3  | VDD_SPI Internal and Output Characteristics                  | 64 |

| 5-4  | DC Characteristics (3.3 V, 25 °C)                            | 64 |

| 5-5  | ADC Characteristics                                          | 65 |

| 5-6  | ADC Calibration Results                                      | 65 |

| 5-7  | Wi-Fi Current Consumption Depending on RF Modes              | 65 |

| 5-8  | Current Consumption in Modem-sleep Mode                      | 66 |

| 5-9  | Current Consumption in Low-Power Modes                       | 67 |

| 5-10 | Reliability Qualifications                                   | 67 |

| 6-1  | Wi-Fi Frequency                                              | 68 |

| 6-2  | TX Power with Spectral Mask and EVM Meeting 802.11 Standards | 68 |

| 6-3  | TX EVM Test                                                  | 68 |

| 6-4  | RX Sensitivity                                               | 70 |

| 6-5  | Maximum RX Level                                             | 70 |

| 6-6  | RX Adjacent Channel Rejection                                | 71 |

| 6-7  | Bluetooth LE Frequency                                       | 71 |

| 6-8  | Transmitter Characteristics - Bluetooth LE 1 Mbps            | 71 |

| 6-9  | Transmitter Characteristics - Bluetooth LE 2 Mbps            | 72 |

|      | Transmitter Characteristics - Bluetooth LE 125 Kbps          | 72 |

|      | Transmitter Characteristics - Bluetooth LE 500 Kbps          | 72 |

|      | Receiver Characteristics - Bluetooth LE 1 Mbps               | 73 |

| 6-13 | Receiver Characteristics - Bluetooth LE 2 Mbps               | 74 |

| 6-14 Receiver Characteristics - Bluetooth LE 125 Kbps | 74 |

|-------------------------------------------------------|----|

| 6-15 Receiver Characteristics - Bluetooth LE 500 Kbps | 75 |

# List of Figures

| 1-1 | ESP32-S3 Series Nomenclature                              | 13 |

|-----|-----------------------------------------------------------|----|

| 2-1 | ESP32-S3 Pin Layout (Top View)                            | 14 |

| 2-2 | ESP32-S3 Power Scheme                                     | 27 |

| 2-3 | Visualization of Timing Parameters for Power-up and Reset | 27 |

| 3-1 | Visualization of Timing Parameters for the Strapping Pins | 30 |

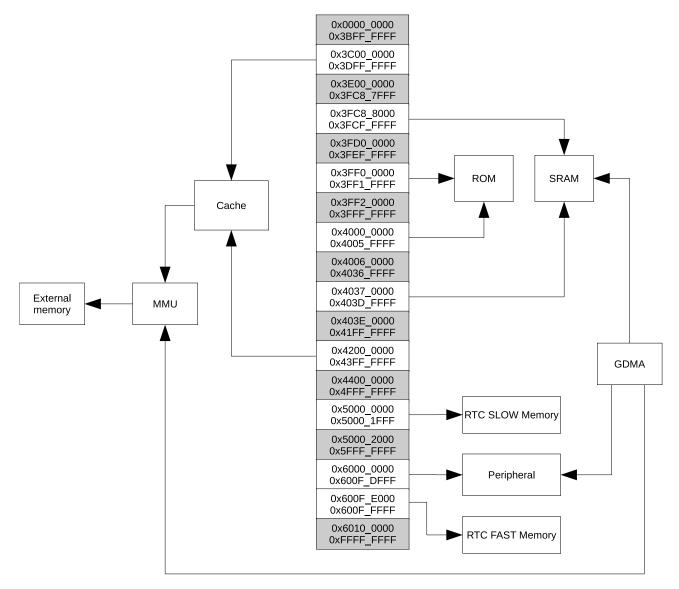

| 4-1 | Address Mapping Structure                                 | 35 |

| 4-2 | Components and Power Domains                              | 41 |

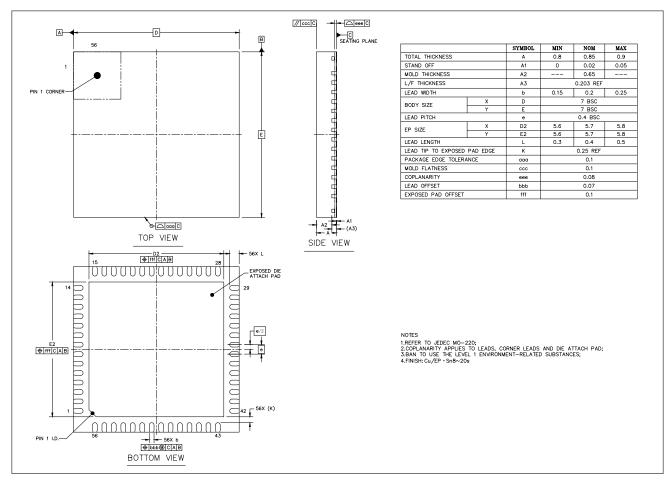

| 7-1 | QFN56 (7×7 mm) Package                                    | 76 |

| 7-2 | QFN56 (7×7 mm) Package (Only for ESP32-S3FH4R2)           | 77 |

# 1 ESP32-S3 Series Comparison

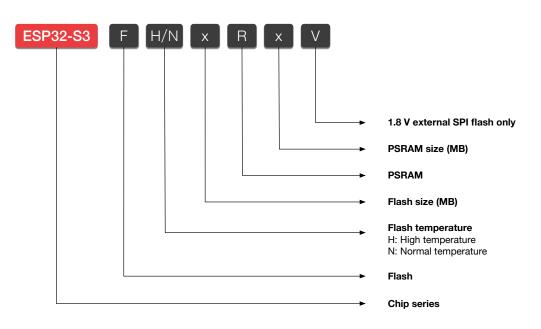

### 1.1 Nomenclature

## 1.2 Comparison

| Ordering Code <sup>1</sup> | In-Package Flash <sup>2</sup> | In-Package PSRAM  | Ambient Temp. <sup>3</sup> (°C) | VDD_SPI Voltage <sup>4</sup> |

|----------------------------|-------------------------------|-------------------|---------------------------------|------------------------------|

| ESP32-S3                   | _                             | _                 | -40 ~ 105                       | 3.3 V/1.8 V                  |

| ESP32-S3FN8                | 8 MB (Quad SPI) <sup>5</sup>  | —                 | -40 ~ 85                        | 3.3 V                        |

| ESP32-S3R2                 | _                             | 2 MB (Quad SPI)   | -40 ~ 85                        | 3.3 V                        |

| ESP32-S3R8                 | _                             | 8 MB (Octal SPI)  | -40 ~ 65                        | 3.3 V                        |

| ESP32-S3R8V                | _                             | 8 MB (Octal SPI)  | -40 ~ 65                        | 1.8 V                        |

| ESP32-S3R16V               | —                             | 16 MB (Octal SPI) | -40 ~ 65                        | 1.8 V                        |

| ESP32-S3FH4R2              | 4 MB (Quad SPI)               | 2 MB (Quad SPI)   | -40 ~ 85                        | 3.3 V                        |

Table 1-1. ESP32-S3 Series Comparison

<sup>1</sup> For details on chip marking and packing, see Section 7 *Packaging*.

<sup>2</sup> By default, the SPI flash on the chip operates at a maximum clock frequency of 80 MHz and does not support the auto suspend feature. If you have a requirement for a higher flash clock frequency of 120 MHz or if you need the flash auto suspend feature, please <u>contact us</u>.

<sup>3</sup> Ambient temperature specifies the recommended temperature range of the environment immediately outside an Espressif chip. For chips with Octal SPI PSRAM (ESP32-S3R8, ESP32-S3R8V, and ESP32-S3R16V), if the PSRAM ECC function is enabled, the maximum ambient temperature can be improved to 85 °C, while the usable size of PSRAM will be reduced by 1/16.

<sup>4</sup> For more information on VDD\_SPI, see Section 2.5 *Power Supply*.

<sup>5</sup> For details about SPI modes, see Section 2.6 *Pin Mapping Between Chip and Flash/PSRAM*.

# 2 Pins

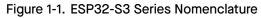

# 2.1 Pin Layout

Figure 2-1. ESP32-S3 Pin Layout (Top View)

### 2.2 Pin Overview

The ESP32-S3 chip integrates multiple peripherals that require communication with the outside world. To keep the chip package size reasonably small, the number of available pins has to be limited. So the only way to route all the incoming and outgoing signals is through pin multiplexing. Pin muxing is controlled via software programmable registers (see <u>ESP32-S3 Technical Reference Manual</u> > Chapter *IO MUX and GPIO Matrix*).

All in all, the ESP32-S3 chip has the following types of pins:

- IO pins with the following predefined sets of functions to choose from:

- Each IO pin has predefined IO MUX functions see Table 2-4 IO MUX Pin Functions

- Some IO pins have predefined RTC functions see Table 2-6 RTC Functions

- Some IO pins have predefined analog functions see Table 2-8 Analog Functions

Predefined functions means that each IO pin has a set of direct connections to certain on-chip components. During run-time, the user can configure which component from a predefined set to connect to a certain pin at a certain time via memory mapped registers (see <u>ESP32-S3 Technical Reference Manual</u> > Chapter IO MUX and GPIO pins).

- Analog pins that have exclusively-dedicated analog functions see Table 2-9 Analog Pins

- Power pins that supply power to the chip components and non-power pins see Table 2-10 Power Pins

Table 2-1 *Pin Overview* gives an overview of all the pins. For more information, see the respective sections for each pin type below, or *Appendix A – ESP32-S3 Consolidated Pin Overview*.

| Pin | Pin     | Pin               | Pin Providing        | Pin Settings <sup>7</sup> Pin Function Sets <sup>1,2</sup> |             |        | ets <sup>1,2</sup> |        |

|-----|---------|-------------------|----------------------|------------------------------------------------------------|-------------|--------|--------------------|--------|

| No. | Name    | Type <sup>1</sup> | Power <sup>3-6</sup> | At Reset                                                   | After Reset | IO MUX | RTC                | Analog |

| 1   | LNA_IN  | Analog            |                      |                                                            |             |        |                    |        |

| 2   | VDD3P3  | Power             |                      |                                                            |             |        |                    |        |

| 3   | VDD3P3  | Power             |                      |                                                            |             |        |                    |        |

| 4   | CHIP_PU | Analog            | VDD3P3_RTC           |                                                            |             |        |                    |        |

| 5   | GPI00   | 10                | VDD3P3_RTC           | IE, WPU                                                    | IE, WPU     | IO MUX | RTC                |        |

| 6   | GPI01   | 10                | VDD3P3_RTC           | IE                                                         | IE          | IO MUX | RTC                | Analog |

| 7   | GPIO2   | 10                | VDD3P3_RTC           | IE                                                         | IE          | IO MUX | RTC                | Analog |

| 8   | GPIO3   | 10                | VDD3P3_RTC           | IE                                                         | IE          | IO MUX | RTC                | Analog |

| 9   | GPIO4   | 10                | VDD3P3_RTC           |                                                            |             | IO MUX | RTC                | Analog |

| 10  | GPI05   | IO                | VDD3P3_RTC           |                                                            |             | IO MUX | RTC                | Analog |

| 11  | GPI06   | IO                | VDD3P3_RTC           |                                                            |             | IO MUX | RTC                | Analog |

| 12  | GPI07   | IO                | VDD3P3_RTC           |                                                            |             | IO MUX | RTC                | Analog |

| 13  | GPI08   | IO                | VDD3P3_RTC           |                                                            |             | IO MUX | RTC                | Analog |

| 14  | GPI09   | IO                | VDD3P3_RTC           |                                                            | IE          | IO MUX | RTC                | Analog |

| 15  | GPIO10  | IO                | VDD3P3_RTC           |                                                            | IE          | IO MUX | RTC                | Analog |

| 16  | GPIO11  | IO                | VDD3P3_RTC           |                                                            | IE          | IO MUX | RTC                | Analog |

| 17  | GPI012  | IO                | VDD3P3_RTC           |                                                            | IE          | IO MUX | RTC                | Analog |

| 18  | GPIO13  | 10                | VDD3P3_RTC           |                                                            | IE          | IO MUX | RTC                | Analog |

#### Table 2-1. Pin Overview

Cont'd on next page

| Pin      | Table 2-1 – cont'd from previous page       Pin     Pin     Pin Providing     Pin Settings <sup>7</sup> Pin Function Sets <sup>1,2</sup> |                   |                          |          |                 |          | ets <sup>1,2</sup> |        |

|----------|------------------------------------------------------------------------------------------------------------------------------------------|-------------------|--------------------------|----------|-----------------|----------|--------------------|--------|

| No.      | Name                                                                                                                                     | Type <sup>1</sup> | Power <sup>3-6</sup>     | At Reset | After Reset     |          |                    | Analog |

| 19       | GPIO14                                                                                                                                   | 19pe<br>10        |                          | ALRESEL  | IE              | IO MUX   | RTC                | •      |

|          | VDD3P3_RTC                                                                                                                               | Power             | VDD3P3_RTC               |          | IC              |          | RIC                | Analog |

| 20<br>21 | XTAL_32K_P                                                                                                                               | IO                | VDD3P3_RTC               |          |                 |          | RTC                | Apolog |

|          |                                                                                                                                          | -                 | _                        |          |                 |          |                    | Analog |

| 22       | XTAL_32K_N<br>GPI017                                                                                                                     | 10                | VDD3P3_RTC<br>VDD3P3 RTC |          | IE              |          | RTC<br>RTC         | Analog |

| 23       |                                                                                                                                          | 10                | _                        |          |                 |          |                    | Analog |

| 24       | GPIO18<br>GPIO19                                                                                                                         | 10                | VDD3P3_RTC               |          | IE              | IO MUX   | RTC                | Analog |

| 25       |                                                                                                                                          | 10                | VDD3P3_RTC               |          |                 |          | RTC                | Analog |

| 26       | GPIO20                                                                                                                                   | 10                | VDD3P3_RTC               | USB_PU   | USB_PU          |          | RTC                | Analog |

| 27       | GPIO21                                                                                                                                   | 10                | VDD3P3_RTC               |          |                 |          | RTC                |        |

| 28       | SPICS1                                                                                                                                   | 10                | VDD_SPI                  | IE, WPU  | IE, WPU         | IO MUX   |                    |        |

| 29       | VDD_SPI                                                                                                                                  | Power             |                          |          |                 | 10.1411/ |                    |        |

| 30       | SPIHD                                                                                                                                    | 10                | VDD_SPI                  | IE, WPU  | IE, WPU         | IO MUX   |                    |        |

| 31       | SPIWP                                                                                                                                    | 10                | VDD_SPI                  | IE, WPU  | IE, WPU         | IO MUX   |                    |        |

| 32       | SPICSO                                                                                                                                   | 10                | VDD_SPI                  | IE, WPU  | IE, WPU         | IO MUX   |                    |        |

| 33       | SPICLK                                                                                                                                   | 10                | VDD_SPI                  | IE, WPU  | IE, WPU         | IO MUX   |                    |        |

| 34       | SPIQ                                                                                                                                     | 10                | VDD_SPI                  | IE, WPU  | IE, WPU         | IO MUX   |                    |        |

| 35       | SPID                                                                                                                                     | 10                | VDD_SPI                  | IE, WPU  | IE, WPU         | IO MUX   |                    |        |

| 36       | SPICLK_N                                                                                                                                 | 10                | VDD_SPI / VDD3P3_CPU     | IE       | IE              | IO MUX   |                    |        |

| 37       | SPICLK_P                                                                                                                                 | 10                | VDD_SPI / VDD3P3_CPU     | IE       | IE              | IO MUX   |                    |        |

| 38       | GPIO33                                                                                                                                   | 10                | VDD_SPI / VDD3P3_CPU     |          | IE              | IO MUX   |                    |        |

| 39       | GPIO34                                                                                                                                   | 10                | VDD_SPI / VDD3P3_CPU     |          | IE              | IO MUX   |                    |        |

| 40       | GPIO35                                                                                                                                   | IO                | VDD_SPI / VDD3P3_CPU     |          | IE              | IO MUX   |                    |        |

| 41       | GPIO36                                                                                                                                   | IO                | VDD_SPI / VDD3P3_CPU     |          | IE              | IO MUX   |                    |        |

| 42       | GPIO37                                                                                                                                   | 10                | VDD_SPI / VDD3P3_CPU     |          | IE              | IO MUX   |                    |        |

| 43       | GPIO38                                                                                                                                   | 10                | VDD3P3_CPU               |          | IE              | IO MUX   |                    |        |

| 44       | MTCK                                                                                                                                     | 10                | VDD3P3_CPU               |          | IE <sup>8</sup> | IO MUX   |                    |        |

| 45       | MTDO                                                                                                                                     | 10                | VDD3P3_CPU               |          | IE              | IO MUX   |                    |        |

| 46       | VDD3P3_CPU                                                                                                                               | Power             |                          |          |                 |          |                    |        |

| 47       | MTDI                                                                                                                                     | 10                | VDD3P3_CPU               |          | IE              | IO MUX   |                    |        |

| 48       | MTMS                                                                                                                                     | 10                | VDD3P3_CPU               |          | IE              | IO MUX   |                    |        |

| 49       | UOTXD                                                                                                                                    | 10                | VDD3P3_CPU               | IE, WPU  | IE, WPU         | IO MUX   |                    |        |

| 50       | UORXD                                                                                                                                    | IO                | VDD3P3_CPU               | IE, WPU  | IE, WPU         | IO MUX   |                    |        |

| 51       | GPIO45                                                                                                                                   | IO                | VDD3P3_CPU               | IE, WPD  | IE, WPD         | IO MUX   |                    |        |

| 52       | GPIO46                                                                                                                                   | IO                | VDD3P3_CPU               | IE, WPD  | IE, WPD         | IO MUX   |                    |        |

| 53       | XTAL_N                                                                                                                                   | Analog            |                          |          |                 |          |                    |        |

| 54       | XTAL_P                                                                                                                                   | Analog            |                          |          |                 |          |                    |        |

| 55       | VDDA                                                                                                                                     | Power             |                          |          |                 |          |                    |        |

| 56       | VDDA                                                                                                                                     | Power             |                          |          |                 |          |                    |        |

| 57       | GND                                                                                                                                      | Power             |                          |          |                 |          |                    |        |

#### Table 2-1 – cont'd from previous page

1. For more information, see respective sections below. Alternatively, see Appendix A – ESP32-S3 Consolidated Pin Overview.

2. Bold marks the pin function set in which a pin has its default function in the default boot mode. For more information about the boot mode, see Section 3.1 *Chip Boot Mode Control*.

3. In column Pin Providing Power, regarding pins powered by VDD\_SPI:

- Power actually comes from the internal power rail supplying power to VDD\_SPI. For details, see Section 2.5.2 Power Scheme.

- 4. In column Pin Providing Power, regarding pins powered by VDD3P3\_CPU / VDD\_SPI:

- Pin Providing Power (either VDD3P3\_CPU or VDD\_SPI) is decided by eFuse bit EFUSE\_PIN\_POWER\_SELECTION (see <u>ESP32-S3 Technical Reference Manual</u> > Chapter eFuse Controller) and can be configured via the IO\_MUX\_PAD\_POWER\_CTRL bit (see <u>ESP32-S3 Technical Reference Manual</u> > Chapter IO MUX and GPIO pins).

- 5. For ESP32-S3R8V chip, as the VDD\_SPI voltage has been set to 1.8 V, the working voltage for pins SPICLK\_N and SPICLK\_P (GPI047 and GPI048) would also be 1.8 V, which is different from other GPI0s.

- 6. The default drive strengths for each pin are as follows:

- GPI017 and GPI018: 10 mA

- GPI019 and GPI020: 40 mA

- All other pins: 20 mA

- 7. Column Pin Settings shows predefined settings at reset and after reset with the following abbreviations:

- IE input enabled

- WPU internal weak pull-up resistor enabled

- WPD internal weak pull-down resistor enabled

- USB\_PU USB pull-up resistor enabled

- By default, the USB function is enabled for USB pins (i.e., GPI019 and GPI020), and the pin pull-up is decided by the USB pull-up. The USB pull-up is controlled by USB\_SERIAL\_JTAG\_DP/DM\_PULLUP and the pull-up resistor value is controlled by USB\_SERIAL\_JTAG\_PULLUP\_VALUE. For details, see <u>ESP32-S3 Technical Reference Manual</u> > Chapter USB Serial/JTAG Controller).

- When the USB function is disabled, USB pins are used as regular GPIOs and the pin's internal weak pull-up and pull-down resistors are disabled by default (configurable by IO\_MUX\_FUN\_WPU/WPD). For details, see <u>ESP32-S3 Technical Reference Manual</u> > Chapter IO MUX and GPIO Matrix.

- 8. Depends on the value of EFUSE\_DIS\_PAD\_JTAG

- 0 WPU is enabled

- 1 pin floating

Some pins have glitches during power-up. See details in Table 2-2.

| Pin        | Glitch <sup>1</sup> | Typical Time Period ( $\mu$ s) |

|------------|---------------------|--------------------------------|

| GPI01      | Low-level glitch    | 60                             |

| GPIO2      | Low-level glitch    | 60                             |

| GPIO3      | Low-level glitch    | 60                             |

| GPIO4      | Low-level glitch    | 60                             |

| GPI05      | Low-level glitch    | 60                             |

| GPIO6      | Low-level glitch    | 60                             |

| GPI07      | Low-level glitch    | 60                             |

| GPIO8      | Low-level glitch    | 60                             |

| GPIO9      | Low-level glitch    | 60                             |

| GPI010     | Low-level glitch    | 60                             |

| GPIO11     | Low-level glitch    | 60                             |

| GPI012     | Low-level glitch    | 60                             |

| GPIO13     | Low-level glitch    | 60                             |

| GPIO14     | Low-level glitch    | 60                             |

| XTAL_32K_P | Low-level glitch    | 60                             |

| XTAL_32K_N | Low-level glitch    | 60                             |

| GPI017     | Low-level glitch    | 60                             |

Cont'd on next page

| Pin    | Glitch <sup>1</sup>            | Typical Time Period ( $\mu$ s) |

|--------|--------------------------------|--------------------------------|

| GPIO18 | Low-level glitch               | 60                             |

|        | High-level glitch              | 60                             |

| GPIO19 | Low-level glitch               | 60                             |

|        | High-level glitch <sup>2</sup> | 60                             |

| GPI020 | Pull-down glitch               | 60                             |

|        | High-level glitch <sup>2</sup> | 60                             |

#### Table 2-2 – cont'd from previous page

<sup>1</sup> Low-level glitch: the pin is at a low level output status during the time period;

High-level glitch: the pin is at a high level output status during the time period;

Pull-down glitch: the pin is at an internal weak pulled-down status during the time period; Pull-up glitch: the pin is at an internal weak pulled-up status during the time period.

Please refer to Table 5-4 *DC Characteristics (3.3 V, 25 °C)* for detailed parameters about low/high-level and pull-down/up.

<sup>2</sup> GPIO19 and GPIO20 pins both have two high-level glitches during chip power-up, each lasting for about 60  $\mu$ s. The total duration for the glitches and the delay are 3.2 ms and 2 ms respectively for GPIO19 and GPIO20.

# 2.3 IO Pins

#### 2.3.1 IO MUX Functions

The IO MUX allows multiple input/output signals to be connected to a single input/output pin. Each IO pin of ESP32-S3 can be connected to one of the five signals (IO MUX functions, i.e., FO-F4), as listed in Table 2-4 *IO MUX Pin Functions*.

Among the five sets of signals:

- Some are routed via the GPIO Matrix (GPIOO, GPIO1, etc.), which incorporates internal signal routing circuitry for mapping signals programmatically. It gives the pin access to almost any peripheral signals. However, the flexibility of programmatic mapping comes at a cost as it might affect the latency of routed signals. For details about connecting to peripheral signals via GPIO Matrix, see *ESP32-S3 Technical Reference Manual* > Chapter *IO MUX and GPIO Matrix*.

- Some are directly routed from certain peripherals (UOTXD, MTCK, etc.), including UARTO/1, JTAG, SPIO/1, and SPI2 see Table 2-3 Peripheral Signals Routed via IO MUX.

| Pin Function     | Signal                | Description                                                             |

|------------------|-----------------------|-------------------------------------------------------------------------|

| UTXD             | Transmit data         |                                                                         |

| URXD             | Receive data          |                                                                         |

| URTS             | Request to send       | UARTO/1 interface                                                       |

| UCTS             | Clear to send         |                                                                         |

| МТСК             | Test clock            |                                                                         |

| MTDO             | Test Data Out         | ITAC interface for debugging                                            |

| MTDI             | Test Data In          | JTAG interface for debugging                                            |

| MTMS             | Test Mode Select      |                                                                         |

| SPIQ             | Data out              |                                                                         |

| SPID             | Data in               | SPI0/1 interface (powered by VDD_SPI) for connection to in-package or   |

| SPIHD            | Hold                  | off-package flash/PSRAM via the SPI bus. It supports 1-, 2-, 4-line SPI |

| SPIWP            | Write protect         | modes. See also Section 2.6 Pin Mapping Between Chip and                |

| SPICLK           | Clock                 | Flash/PSRAM                                                             |

| SPICS            | Chip select           |                                                                         |

| SPIIO            | Data                  | SPI0/1 interface (powered by VDD_SPI or VDD3P3_CPU) for the higher      |

| SPIDQS           | Data strobe/data mask | 4 bits data line interface and DQS interface in 8-line SPI mode         |

| SPICLK_N_DIFF    | Negative clock signal | Differential clock negative/positive for the SPI bus                    |

| SPICLK_P_DIFF    | Positive clock signal |                                                                         |

| SUBSPIQ          | Data out              |                                                                         |

| SUBSPID          | Data in               | CDIO (1 interface (neuronal bus) (DD2D2, DTO or ) (DD2) (2, ODI I) for  |

| SUBSPIHD         | Hold                  | SPI0/1 interface (powered by VDD3P3_RTC or VDD3V3_CPU) for              |

| SUBSPIWP         | Write protect         | connection to in-package or off-package flash/PSRAM via the SUBSPI      |

| SUBSPICLK        | Clock                 | bus. It supports 1-, 2-, 4-line SPI modes                               |

| SUBSPICS         | Chip select           |                                                                         |

| SUBSPICLK_N_DIFF | Negative clock signal | Differential clock negative/positive for the SUBSPI bus                 |

| SUBSPICLK_P_DIFF | Positive clock signal |                                                                         |

#### Table 2-3. Peripheral Signals Routed via IO MUX

Cont'd on next page

| Pin Function | Signal                | Description                                                                |  |  |  |  |  |

|--------------|-----------------------|----------------------------------------------------------------------------|--|--|--|--|--|

| FSPIQ        | Data out              |                                                                            |  |  |  |  |  |

| FSPID        | Data in               |                                                                            |  |  |  |  |  |

| FSPIHD       | Hold                  | SPI2 interface for fast SPI connection. It supports 1-, 2-, 4-line SPI     |  |  |  |  |  |

| FSPIWP       | Write protect         | modes                                                                      |  |  |  |  |  |

| FSPICLK      | Clock                 |                                                                            |  |  |  |  |  |

| FSPICSO      | Chip select           |                                                                            |  |  |  |  |  |

| FSPIIO       | Data                  | The higher 4 bits data line interface and DQS interface for SPI2 interface |  |  |  |  |  |

| FSPIDQS      | Data strobe/data mask | in 8-line SPI mode                                                         |  |  |  |  |  |

| CLK_OUT      | Clock output          | Output clock signals generated by the chip's internal components           |  |  |  |  |  |

Table 2-3 – cont'd from previous page

Table 2-4 IO MUX Pin Functions shows the IO MUX functions of IO pins.

| Table 2-4. | IO MUX Pin    | Functions |

|------------|---------------|-----------|

|            | 10 1110/11 11 |           |

| Pin | IO MUX /                  |        |                   |        |       | IO MUX Fu | nc | tion <sup>1, 2,</sup> | 3         |        |                |        |

|-----|---------------------------|--------|-------------------|--------|-------|-----------|----|-----------------------|-----------|--------|----------------|--------|

| No. | GPIO<br>Name <sup>2</sup> | FO     | Type <sup>3</sup> | F1     | Туре  | F2        |    | Туре                  | F3        | Туре   | F4             | Туре   |

| 5   | GPIOO                     | GPIOO  | I/0/T             | GPI00  | 1/0/T |           |    |                       |           |        |                |        |

| 6   | GPI01                     | GPIO1  | 1/0/T             | GPI01  | 1/0/T |           |    |                       |           |        |                |        |

| 7   | GPIO2                     | GPIO2  | 1/0/T             | GPIO2  | 1/0/T |           |    |                       |           |        |                |        |

| 8   | GPIO3                     | GPIO3  | I/0/T             | GPIO3  | 1/0/T |           |    |                       |           |        |                |        |

| 9   | GPIO4                     | GPIO4  | I/0/T             | GPIO4  | 1/0/T |           |    |                       |           |        |                |        |

| 10  | GPI05                     | GPI05  | I/0/T             | GPI05  | 1/0/T |           |    |                       |           |        |                |        |

| 11  | GPIO6                     | GPIO6  | I/0/T             | GPIO6  | 1/0/T |           |    |                       |           |        |                |        |

| 12  | GPI07                     | GPIO7  | I/0/T             | GPI07  | 1/0/T |           |    |                       |           | 1d     |                |        |

| 13  | GPI08                     | GPIO8  | I/0/T             | GPI08  | 1/0/T |           |    |                       | SUBSPICS1 | 0/T    |                | lc     |

| 14  | GPIO9                     | GPIO9  | I/0/T             | GPI09  | 1/0/T |           | 4g |                       | SUBSPIHD  | 11/0/T | FSPIHD         | 11/0/T |

| 15  | GPI010                    | GPIO10 | I/0/T             | GPIO10 | I/O/T | FSPII04   |    | 11/0/T                | SUBSPICSO | O/T    | <b>FSPICSO</b> | 11/0/T |

| 16  | GPIO11                    | GPIO11 | I/0/T             | GPIO11 | 1/0/T | FSPII05   |    | 11/0/T                | SUBSPID   | 11/0/T | FSPID          | 11/0/T |

| 17  | GPI012                    | GPIO12 | I/0/T             | GPI012 | 1/0/T | FSPII06   |    | 11/0/T                | SUBSPICLK | O/T    | FSPICLK        | 11/0/T |

| 18  | GPIO13                    | GPIO13 | I/0/T             | GPIO13 | 1/0/T | FSPII07   |    | 11/0/T                | SUBSPIQ   | 11/0/T | FSPIQ          | 11/0/T |

| 19  | GPI014                    | GPIO14 | I/0/T             | GPIO14 | 1/0/T | FSPIDQS   |    | O/T                   | SUBSPIWP  | 11/0/T | FSPIWP         | 11/0/T |

| 21  | GPI015                    | GPIO15 | I/0/T             | GPI015 | 1/0/T | UORTS     |    | 0                     |           |        |                |        |

| 22  | GPI016                    | GPIO16 | I/0/T             | GPIO16 | 1/0/T | UOCTS     |    | 11                    |           |        |                |        |

| 23  | GPI017                    | GPIO17 | I/0/T             | GPIO17 | 1/0/T | U1TXD     |    | 0                     |           |        |                |        |

| 24  | GPI018                    | GPIO18 | I/0/T             | GPIO18 | 1/0/T | U1RXD     |    | 11                    | CLK_OUT3  | 0      |                |        |

| 25  | GPI019                    | GPI019 | I/0/T             | GPI019 | I/0/T | U1RTS     |    | 0                     | CLK_OUT2  | 0      |                |        |

| 26  | GPIO20                    | GPIO20 | I/0/T             | GPIO20 | I/0/T | U1CTS     |    | 11                    | CLK_OUT1  | 0      |                |        |

| 27  | GPIO21                    | GPIO21 | I/0/T             | GPIO21 | 1/0/T |           |    |                       |           |        |                |        |

Cont'd on next page

| Pin | IO MUX /                  |                   |                   |        |       | IO MUX Fu         |     |        | 3         |        |        |        |

|-----|---------------------------|-------------------|-------------------|--------|-------|-------------------|-----|--------|-----------|--------|--------|--------|

| No. | GPIO<br>Name <sup>2</sup> | FO 4a             | Type <sup>3</sup> | F1     | Туре  | F2                |     | Туре   | F3        | Туре   | F4     | Туре   |

| 28  | GPIO26                    | SPICS1            | 0/T               | GPIO26 | I/0/T |                   |     |        |           |        |        |        |

| 30  | GPIO27                    | SPIHD             | 11/0/T            | GPIO27 | I/0/T |                   |     |        |           |        |        |        |

| 31  | GPIO28                    | SPIWP             | 11/0/T            | GPIO28 | I/O/T |                   |     |        |           |        |        |        |

| 32  | GPIO29                    | SPICSO            | O/T               | GPIO29 | 1/0/T |                   |     |        |           |        |        |        |

| 33  | GPIO30                    | SPICLK            | O/T               | GPIO30 | 1/0/T |                   |     |        |           |        |        |        |

| 34  | GPIO31                    | SPIQ              | 11/0/T            | GPIO31 | 1/0/T |                   |     |        |           |        |        |        |

| 35  | GPIO32                    | SPID              | 11/0/T            | GPIO32 | 1/0/T |                   | 4f  |        |           | 4e     |        | lb     |

| 38  | GPIO33                    | GPIO33            | 1/0/T             | GPIO33 | 1/0/T | FSPIHD            | _   | 11/0/T | SUBSPIHD  | 11/0/T | SPIIO4 | 11/0/T |

| 39  | GPIO34                    | GPIO34            | 1/0/T             | GPIO34 | 1/0/T | <b>FSPICSO</b>    |     | 11/0/T | SUBSPICSO | O/T    | SPII05 | 11/0/T |

| 40  | GPIO35                    | GPIO35            | 1/0/T             | GPIO35 | 1/0/T | FSPID             |     | 11/0/T | SUBSPID   | 11/0/T | SPIIO6 | 11/0/T |

| 41  | GPIO36                    | GPIO36            | 1/0/T             | GPIO36 | 1/0/T | FSPICLK           |     | 11/0/T | SUBSPICLK | O/T    | SPII07 | 11/0/T |

| 42  | GPIO37                    | GPIO37            | 1/0/T             | GPIO37 | 1/0/T | FSPIQ             |     | 11/0/T | SUBSPIQ   | 11/0/T | SPIDQS | 10/0/T |

| 43  | GPIO38                    | GPIO38            | 1/0/T             | GPIO38 | 1/0/T | FSPIWP            |     | 11/0/T | SUBSPIWP  | 11/0/T |        |        |

| 44  | GPIO39                    | МТСК              | 11                | GPIO39 | 1/0/T | CLK_OUT           | 3   | 0      | SUBSPICS1 | O/T    |        |        |

| 45  | GPIO40                    | MTDO              | O/T               | GPIO40 | 1/0/T | CLK_OUT           | 2   | 0      |           |        |        |        |

| 47  | GPIO41                    | MTDI              | 11                | GPIO41 | 1/0/T | CLK_OUT           | 1   | 0      |           |        |        |        |

| 48  | GPIO42                    | MTMS              | 11                | GPIO42 | 1/0/T |                   |     |        |           |        |        |        |

| 49  | GPIO43                    | UOTXD             | 0                 | GPIO43 | 1/0/T | CLK_OUT           | 1   | 0      |           |        |        |        |

| 50  | GPIO44                    | UORXD             | 11                | GPIO44 | 1/0/T | CLK_OUT           | 2   | 0      |           |        |        |        |

| 51  | GPIO45                    | GPIO45            | 1/0/T             | GPIO45 | 1/0/T |                   |     |        |           |        |        |        |

| 52  | GPIO46                    | GPIO46            | 1/0/T             | GPIO46 | 1/0/T |                   |     |        |           |        |        |        |

| 37  | GPIO47                    | SPI<br>CLK_P_DIFF | O/T               | GPIO47 | I/O/T | SUBSPI<br>CLK_P_D | IFF | 0/T    |           |        |        |        |

| 36  | GPIO48                    | SPI<br>CLK_N_DIFF | 0/T               | GPIO48 | I/0/T | SUBSPI<br>CLK_N_C | IFF | 0/T    |           |        |        |        |

#### Table 2-4 – cont'd from previous page

<sup>1</sup> **Bold** marks the default pin functions in the default boot mode. For more information about the boot mode, see Section 3.1 *Chip Boot Mode Control.*

<sup>2</sup> Regarding highlighted cells, see Section 2.3.4 *Restrictions for GPIOs and RTC\_GPIOs*.

<sup>3</sup> Each IO MUX function (Fn, n = 0 ~ 4) is associated with a type. The description of type is as follows:

- I input. O output. T high impedance.

- I1 input; if the pin is assigned a function other than Fn, the input signal of Fn is always 1.

- IO input; if the pin is assigned a function other than  $F_n$ , the input signal of  $F_n$  is always O.

<sup>4a-4g</sup> For detailed pin assignment of SPI, please refer to 4.2.1.5 Serial Peripheral Interface (SPI) > Pin Assignment.

#### 2.3.2 RTC Functions

When the chip is in Deep-sleep mode, the IO MUX described in Section 2.3.1 *IO MUX Functions* will not work. That is where the RTC IO MUX comes in. It allows multiple input/output signals to be a single input/output pin in Deep-sleep mode, as the pin is connected to the RTC system and powered by VDD3P3\_RTC.

RTC IO pins can be assigned to RTC functions. They can

- Either work as RTC GPIOs (RTC\_GPIOO, RTC\_GPIO1, etc.), connected to the ULP coprocessor

- Or connect to RTC peripheral signals (sar\_i2c\_scl\_0, sar\_i2c\_sda\_0, etc.) see Table 2-5 RTC Peripheral Signals Routed via RTC IO MUX

| Pin Function | Signal       | Description          |

|--------------|--------------|----------------------|

| sar_i2c_scl  | Serial clock | RTC I2CO/1 interface |

| sar_i2c_sda  | Serial data  | RTC 12CO/TIMEHACE    |

Table 2-5. RTC Peripheral Signals Routed via RTC IO MUX

Table 2-6 RTC Functions shows the RTC functions of RTC IO pins.

Table 2-6. RTC Functions

| Pin | RTC                  | RTC Function <sup>2</sup> |    |    | n <sup>2</sup> |

|-----|----------------------|---------------------------|----|----|----------------|

| No. | IO Name <sup>1</sup> | FO                        | F1 | F2 | F3             |

| 5   | RTC_GPIOO            | RTC_GPIOO                 |    |    | sar_i2c_scl_0  |

| 6   | RTC_GPI01            | RTC_GPI01                 |    |    | sar_i2c_sda_0  |

| 7   | RTC_GPIO2            | RTC_GPIO2                 |    |    | sar_i2c_scl_1  |

| 8   | RTC_GPIO3            | RTC_GPIO3                 |    |    | sar_i2c_sda_1  |

| 9   | RTC_GPIO4            | RTC_GPIO4                 |    |    |                |

| 10  | RTC_GPI05            | RTC_GPI05                 |    |    |                |

| 11  | RTC_GPI06            | RTC_GPIO6                 |    |    |                |

| 12  | RTC_GPI07            | RTC_GPI07                 |    |    |                |

| 13  | RTC_GPI08            | RTC_GPIO8                 |    |    |                |

| 14  | RTC_GPI09            | RTC_GPIO9                 |    |    |                |

| 15  | RTC_GPI010           | RTC_GPI010                |    |    |                |

| 16  | RTC_GPI011           | RTC_GPIO11                |    |    |                |

| 17  | RTC_GPI012           | RTC_GPI012                |    |    |                |

| 18  | RTC_GPI013           | RTC_GPI013                |    |    |                |

| 19  | RTC_GPI014           | RTC_GPI014                |    |    |                |

| 21  | RTC_GPI015           | RTC_GPI015                |    |    |                |

| 22  | RTC_GPI016           | RTC_GPI016                |    |    |                |

| 23  | RTC_GPI017           | RTC_GPI017                |    |    |                |

| 24  | RTC_GPI018           | RTC_GPIO18                |    |    |                |

| 25  | RTC_GPI019           | RTC_GPI019                |    |    |                |

| 26  | RTC_GPIO20           | RTC_GPIO20                |    |    |                |

| 27  | RTC_GPIO21           | RTC_GPIO21                |    |    |                |

<sup>1</sup> This column lists the RTC GPIO names, since RTC functions are configured with RTC GPIO registers that use RTC GPIO numbering.

<sup>2</sup> Regarding highlighted cells, see Section 2.3.4 *Restrictions for GPIOs and RTC\_GPIOs*.

### 2.3.3 Analog Functions

Some IO pins also have **analog functions**, for analog peripherals (such as ADC) in any power mode. Internal analog signals are routed to these analog functions, see Table 2-7 *Analog Signals Routed to Analog Functions*.

| Pin Function | Signal                      | Description                          |

|--------------|-----------------------------|--------------------------------------|

| TOUCH        | Touch sensor channel signal | Touch sensor interface               |

| ADCCH        | ADC1/2 channel signal       | ADC1/2 interface                     |

| XTAL_32K_N   | Negative clock signal       | 32 kHz external clock input/output   |

| XTAL_32K_P   | Positive clock signal       | connected to ESP32-S3's oscillator   |

| USB_D-       | Data -                      | USB OTG and USB Serial/JTAG function |

| USB_D+       | Data +                      | USB OTG and USB Senal/STAG function  |

Table 2-7. Analog Signals Routed to Analog Functions

Table 2-8 Analog Functions shows the analog functions of IO pins.

| Pin | Analog                  | Analog Function <sup>3</sup> |          |  |  |  |

|-----|-------------------------|------------------------------|----------|--|--|--|

| No. | IO Name <sup>1, 2</sup> | FO                           | F1       |  |  |  |

| 5   | RTC_GPIOO               |                              |          |  |  |  |

| 6   | RTC_GPI01               | TOUCH1                       | ADC1_CHO |  |  |  |

| 7   | RTC_GPIO2               | TOUCH2                       | ADC1_CH1 |  |  |  |

| 8   | RTC_GPIO3               | TOUCH3                       | ADC1_CH2 |  |  |  |

| 9   | RTC_GPIO4               | TOUCH4                       | ADC1_CH3 |  |  |  |

| 10  | RTC_GPI05               | TOUCH5                       | ADC1_CH4 |  |  |  |

| 11  | RTC_GPI06               | TOUCH6                       | ADC1_CH5 |  |  |  |

| 12  | RTC_GPI07               | TOUCH7                       | ADC1_CH6 |  |  |  |

| 13  | RTC_GPI08               | TOUCH8                       | ADC1_CH7 |  |  |  |

| 14  | RTC_GPI09               | ТОИСНЭ                       | ADC1_CH8 |  |  |  |

| 15  | RTC_GPI010              | TOUCH10                      | ADC1_CH9 |  |  |  |

| 16  | RTC_GPI011              | TOUCH11                      | ADC2_CHO |  |  |  |

| 17  | RTC_GPI012              | TOUCH12                      | ADC2_CH1 |  |  |  |

| 18  | RTC_GPI013              | TOUCH13                      | ADC2_CH2 |  |  |  |

| 19  | RTC_GPI014              | TOUCH14                      | ADC2_CH3 |  |  |  |

| 21  | RTC_GPI015              | XTAL_32K_P                   | ADC2_CH4 |  |  |  |

| 22  | RTC_GPI016              | XTAL_32K_N                   | ADC2_CH5 |  |  |  |

| 23  | RTC_GPI017              |                              | ADC2_CH6 |  |  |  |

| 24  | RTC_GPI018              |                              | ADC2_CH7 |  |  |  |

| 25  | RTC_GPI019              | USB_D-                       | ADC2_CH8 |  |  |  |

| 26  | RTC_GPIO20              | USB_D+                       | ADC2_CH9 |  |  |  |

| 27  | RTC_GPIO21              |                              |          |  |  |  |

#### Table 2-8. Analog Functions

<sup>1</sup> **Bold** marks the default pin functions in the default boot mode. For more information about the boot mode, see Section 3.1 *Chip Boot Mode Control*.

- <sup>2</sup> This column lists the RTC GPIO names, since analog functions are configured with RTC GPIO registers that use RTC GPIO numbering.

- <sup>3</sup> Regarding highlighted cells, see Section 2.3.4 *Restrictions for GPIOs and RTC\_GPIOs*.

### 2.3.4 Restrictions for GPIOs and RTC\_GPIOs

All IO pins of ESP32-S3 have GPIO and some have RTC\_GPIO pin functions. However, the IO pins are multiplexed and can be configured for different purposes based on the requirements. Some IOs have restrictions for usage. It is essential to consider the multiplexed nature and the limitations when using these IO pins.

In tables of this chapter, some pin functions are highlighted. The non-highlighted GPIO or RTC\_GPIO pins are recommended for use first. If more pins are needed, the highlighted GPIOs or RTC\_GPIOs should be chosen carefully to avoid conflicts with important pin functions.

The highlighted IO pins have the following important pin functions:

- GPIO allocated for communication with in-package flash/PSRAM and NOT recommended for other uses. For details, see Section 2.6 *Pin Mapping Between Chip and Flash/PSRAM*.

- GPIO no restrictions, unless the chip is connected to flash/PSRAM using 8-line SPI mode. For details, see Section 2.6 *Pin Mapping Between Chip and Flash/PSRAM*.

- GPIO have one of the following important functions:

- Strapping pins need to be at certain logic levels at startup. See Section 3 Boot Configurations.

- USB\_D+/- by default, connected to the USB Serial/JTAG Controller. To function as GPIOs, these

pins need to be reconfigured via the IO\_MUX\_MCU\_SEL bit (see

ESP32-S3 Technical Reference Manual > Chapter IO MUX and GPIO Matrix for details).

- JTAG interface often used for debugging. See Table 2-4 *IO MUX Pin Functions*. To free these pins up, the pin functions USB\_D+/- of the USB Serial/JTAG Controller can be used instead. See also Section 3.4 *JTAG Signal Source Control*.

- UART interface often used for debugging. See Table 2-4 IO MUX Pin Functions.

See also Appendix A – ESP32-S3 Consolidated Pin Overview.

# 2.4 Analog Pins

#### Table 2-9. Analog Pins

| Pin | Pin     | Pin  | Pin                                                                    |

|-----|---------|------|------------------------------------------------------------------------|

| No. | Name    | Туре | Function                                                               |

| 1   | LNA_IN  | 1/0  | Low Noise Amplifier (RF LNA) input/output signals                      |

|     |         |      | High: on, enables the chip (powered up).                               |

| 4   | CHIP_PU | 1    | Low: off, disables the chip (powered down).                            |

|     |         |      | Note: Do not leave the CHIP_PU pin floating.                           |

| 53  | XTAL_N  | _    | External clock input/output connected to chip's crystal or oscillator. |

| 54  | XTAL_P  | _    | P/N means differential clock positive/negative.                        |

# 2.5 Power Supply

#### 2.5.1 Power Pins

The chip is powered via the power pins described in Table 2-10 Power Pins.

| Pin | Pin         |           | Power Supply <sup>1,2</sup>            |              |

|-----|-------------|-----------|----------------------------------------|--------------|

| No. | Name        | Direction | Power Domain / Other                   | IO Pins $^5$ |

| 2   | VDD3P3      | Input     | Analog power domain                    |              |

| 3   | VDD3P3      | Input     | Analog power domain                    |              |

| 20  | VDD3P3_RTC  | Input     | RTC and part of Digital power domains  | RTC IO       |

| 29  | VDD_SPI 3,4 | Input     | In-package memory (backup power line)  |              |

| 29  | VDD_SPI */  | Output    | In-package and off-package flash/PSRAM | SPI IO       |

| 46  | VDD3P3_CPU  | Input     | Digital power domain                   | Digital IO   |

| 55  | VDDA        | Input     | Analog power domain                    |              |

| 56  | VDDA        | Input     | Analog power domain                    |              |

| 57  | GND         | -         | External ground connection             |              |

#### Table 2-10. Power Pins

<sup>1</sup> See in conjunction with Section 2.5.2 *Power Scheme*.

<sup>2</sup> For recommended and maximum voltage and current, see Section 5.1 Absolute Maximum Ratings and Section 5.2 Recommended Power Supply Characteristics.

- <sup>3</sup> To configure VDD\_SPI as input or output, see <u>ESP32-S3 Technical Reference Manual</u> > Chapter Low-power Management.

- <sup>4</sup> To configure output voltage, see Section 3.2 VDD\_SPI Voltage Control and Section 5.3 VDD\_SPI Output Characteristics.

- <sup>5</sup> RTC IO pins are those powered by VDD3P3\_RTC and so on, as shown in Figure 2-2 *ESP32-S3 Power Scheme*. See also Table 2-1 *Pin Overview* > Column *Pin Providing Power*.

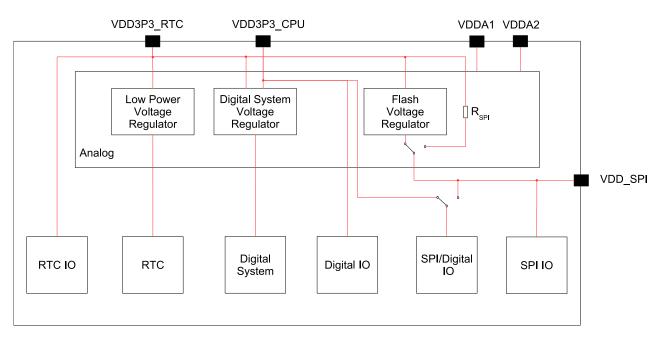

#### 2.5.2 Power Scheme

The power scheme is shown in Figure 2-2 ESP32-S3 Power Scheme.

The components on the chip are powered via voltage regulators.

| Table 2-11. | Voltage | Regulators |

|-------------|---------|------------|

|-------------|---------|------------|

| Voltage Regulator | Output | Power Supply               |

|-------------------|--------|----------------------------|

| Digital           | 1.1 V  | Digital power domain       |

| Low-power         | 1.1 V  | RTC power domain           |

|                   |        | Can be configured to power |

| Flash             | 1.8 V  | in-package flash/PSRAM or  |

|                   |        | off-package memory         |

Figure 2-2. ESP32-S3 Power Scheme

#### 2.5.3 Chip Power-up and Reset

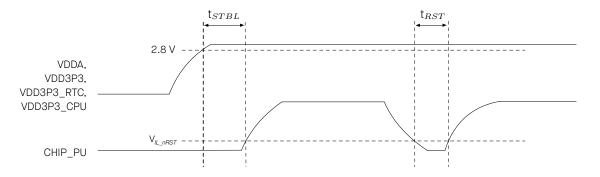

Once the power is supplied to the chip, its power rails need a short time to stabilize. After that, CHIP\_PU – the pin used for power-up and reset – is pulled high to activate the chip. For information on CHIP\_PU as well as power-up and reset timing, see Figure 2-3 and Table 2-12.

Figure 2-3. Visualization of Timing Parameters for Power-up and Reset

| Table 2-12. | Description of | <sup>:</sup> Timing Param             | neters for Power-u | p and Reset |

|-------------|----------------|---------------------------------------|--------------------|-------------|

|             | Beeenpaleri ei | i i i i i i i i i i i i i i i i i i i |                    |             |

| Parameter         | Description                                                        |    |  |  |

|-------------------|--------------------------------------------------------------------|----|--|--|

|                   | Time reserved for the power rails of VDDA, VDD3P3,                 |    |  |  |

| t <sub>STBL</sub> | VDD3P3_RTC, and VDD3P3_CPU to stabilize before the CHIP_PU         |    |  |  |

|                   | pin is pulled high to activate the chip                            |    |  |  |

| +                 | Time reserved for CHIP_PU to stay below $V_{IL_nRST}$ to reset the | 50 |  |  |

| t <sub>RST</sub>  | chip (see Table 5-4)                                               | 50 |  |  |

# 2.6 Pin Mapping Between Chip and Flash/PSRAM

Table 2-13 lists the pin mapping between the chip and flash/PSRAM for all SPI modes.

For chip variants with in-package flash/PSRAM (see Table 1-1 *ESP32-S3 Series Comparison*), the pins allocated for communication with in-package flash/PSRAM can be identified depending on the SPI mode used.

For off-package flash/PSRAM, these are the recommended pin mappings.

For more information on SPI controllers, see also Section 4.2.1.5 Serial Peripheral Interface (SPI).

#### Notice:

It is not recommended to use the pins connected to flash/PSRAM for any other purposes.